### 1.1 GENERAL

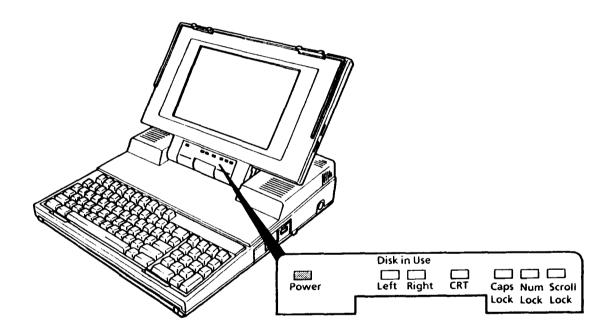

Toshiba Personal Computer T3200 (hereinafter referred to as T3200) is a portable personal computer which is compatible with IBM PC/AT situated at higher rank of portable computer than Toshiba T3100. Hardware of the T3200, a lot of IC chips are C-MOS type so that the power consumption is very little and Gate Array chips are applied so that it is very compact and light weight.

The T3200 is composed of as follows:

System PCB (Printed curcuit board) Hard disk control PCB 3.5-inch floppy disk drive 3.5-inch hard disk drive Plasma display Keyboard Power supply unit

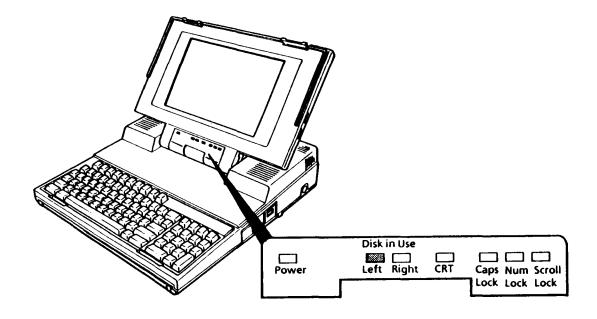

FIGURE 1-1 T3200 Personal Computer

A 3.5-inch Floppy disk drive (FDD) is double-sided, double-density, double-track with storage capacity of 720 kilobytes (formatted). A 3.5-inch hard disk drive (HDD) with storage capacity of 40 megabytes (formatted) is the second external storage device. The plasma display with pixels of 720 in columns and 400 in rows.

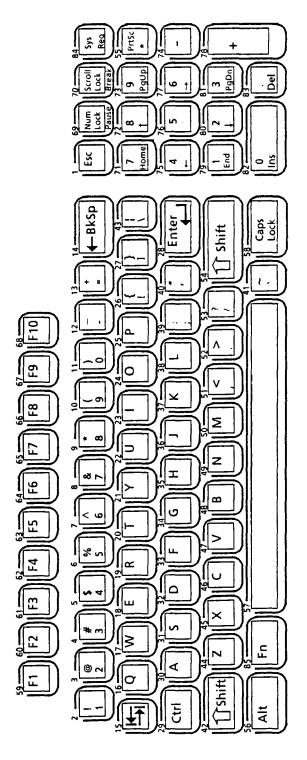

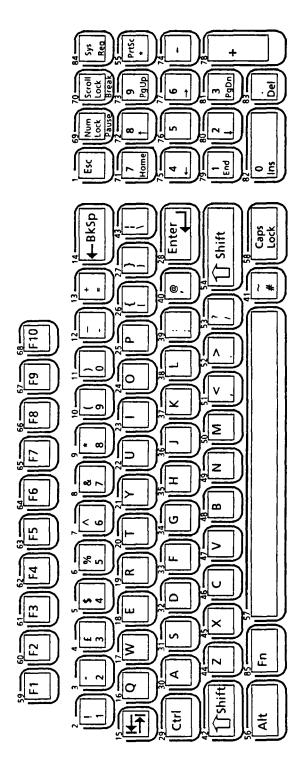

The keyboard has 85 keys. For most applications it can be used exactly like a standard typewriter keyboard.

The power supply unit provides +5 Vdc and  $\pm 12$  Vdc power to every component in the system unit, including the option cards. For the plasma display, this unit regulates  $\pm 205$  Vdc power. This unit has a ventilation fan, driven by  $\pm 12$  Vdc. The fan enhances the reliability and durability of the T3200 system unit.

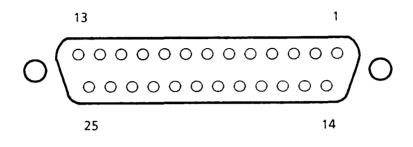

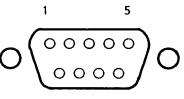

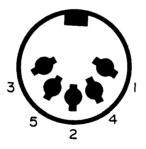

The T3200 provided connecting to the optional devices at the rear panel of the system. There are three connectors such as a parallel printer (or an external floppy disk drive), an RGB direct drive CRT display and an RS-232C device.

The connector for a parallel printer can be used to connect an external FDD unit by changing the A-B-PRT switch setting.

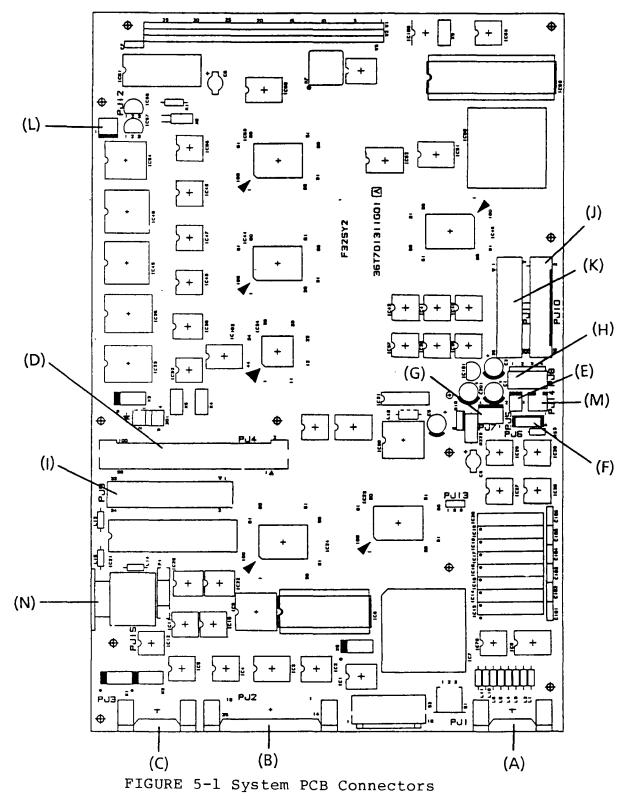

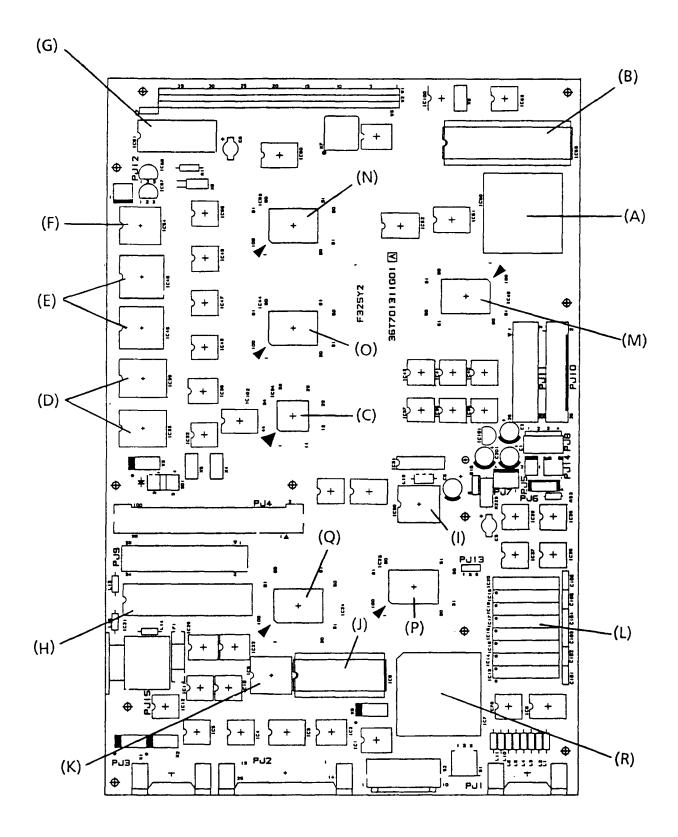

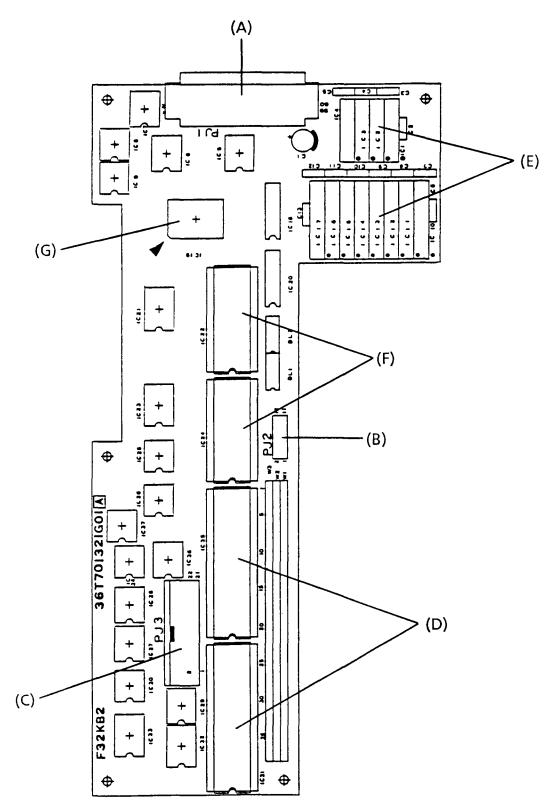

#### 1.2 SYSTEM PCB

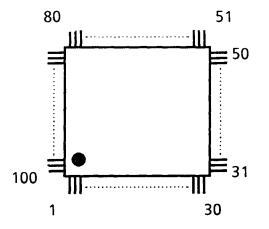

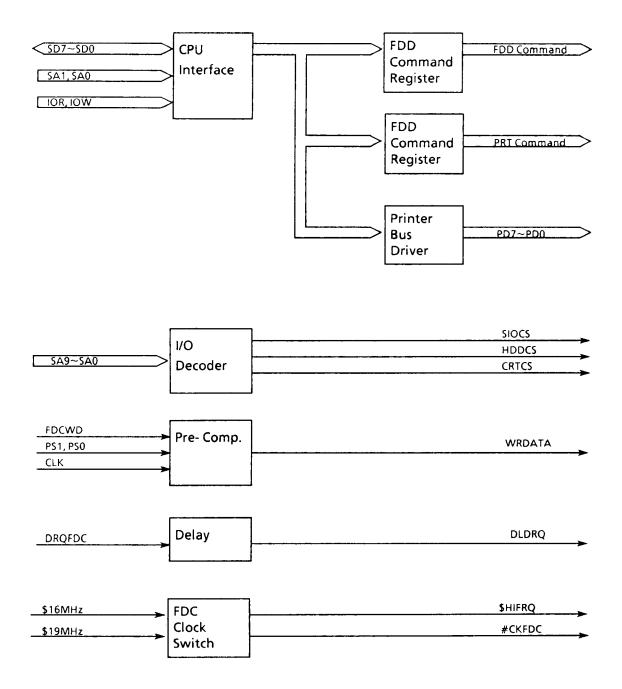

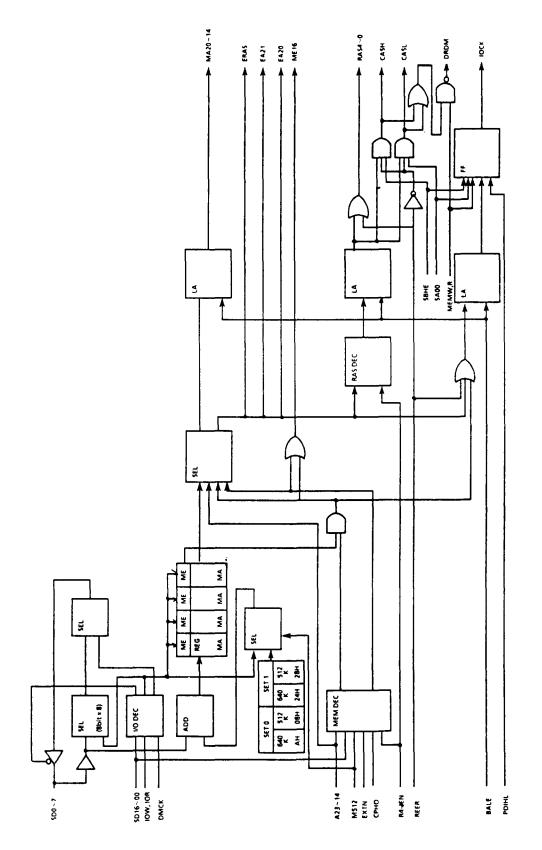

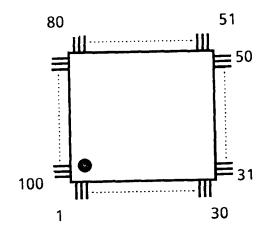

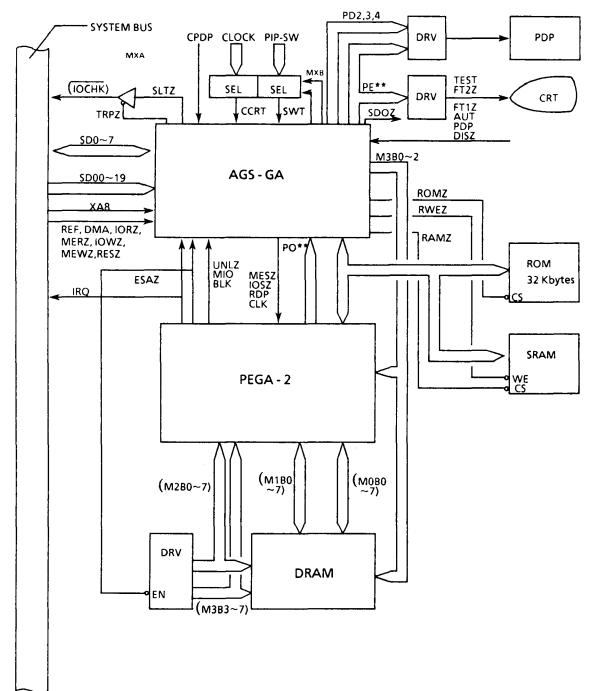

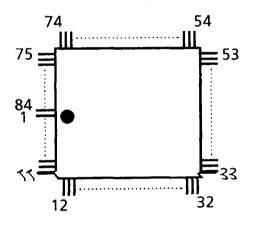

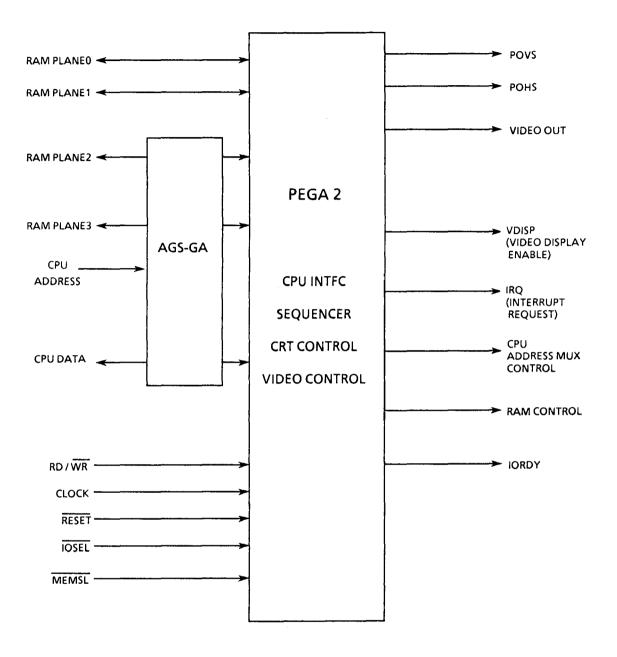

System PCB is composed of the following devices:

Central processor: CPU (80286-12) (12 MHz/6 MHz)) 0 Numeric data processor: NPU (80287, optional) 0 0 Memory RAM 1 Mbyte standard . . . . . . . . . . . . . . . . . 3 Mbytes (option card) --- "LIM" standard ROM (Main BIOS) .... 64 Kbytes (16 bits) (AGS BIOS) ..... 32 Kbytes (8 bits) Video RAM ..... 256 Kbytes System support elements 0 Direct memory access: DMA (82C37) Programmable interrupt controller: PIC (82C59) Programmable interval timer: PIT (82C54) Real time clock: RTC (MC146818) Floppy disk controller: FDC (TC8565F) 0 Keyboard controller: KBC (u8042) x 2 0 Display controller: PEGA2, AGS G.A. 0 Gate array 0

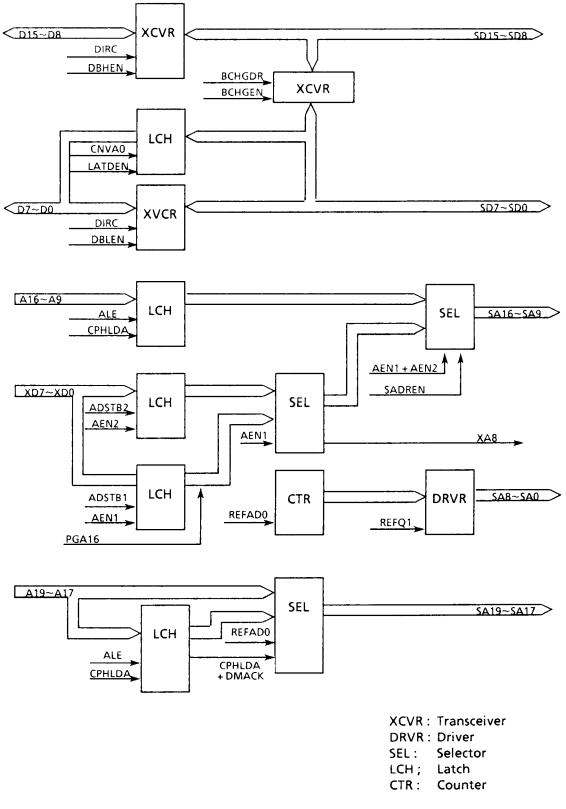

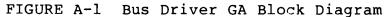

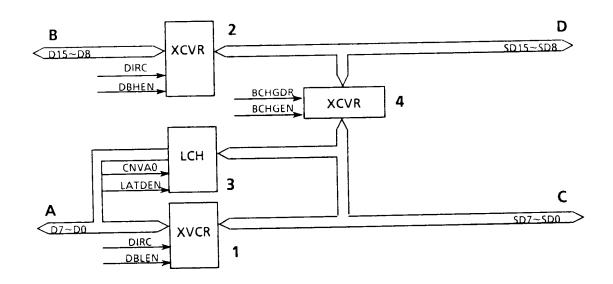

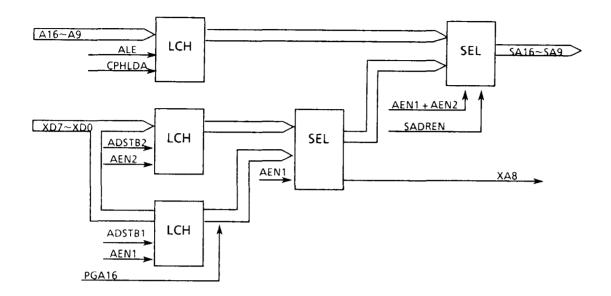

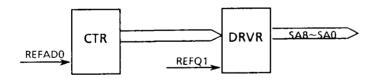

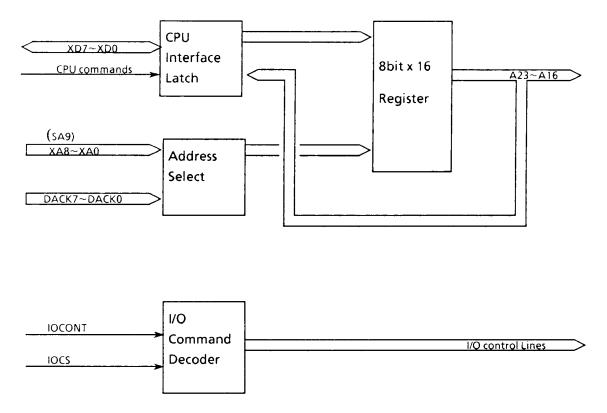

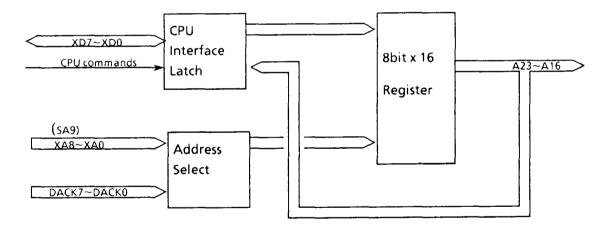

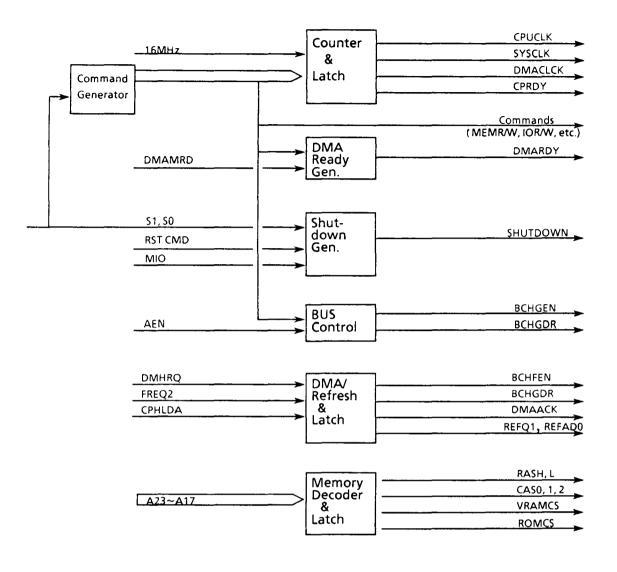

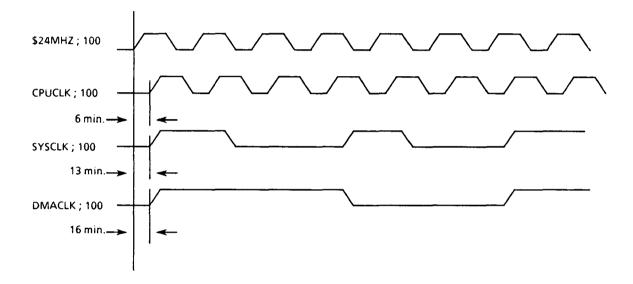

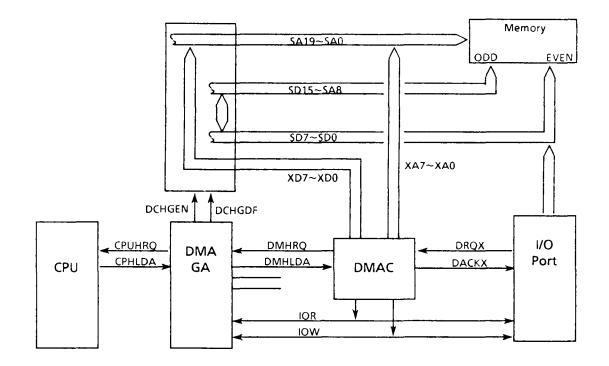

Bus driver Memory mapper DMA driver I/O controller LIM AGS (Advanced graphics subsystem)

### 1.2.1 DIP switches

The system has DIP switches which are located at the rear panel. The following table shows function of the DIP switches.

| DIP<br>Switch | Setting    | Description                             |  |  |  |

|---------------|------------|-----------------------------------------|--|--|--|

| ON            |            | Auto-Switched display mode              |  |  |  |

| 1             | OFF        | IBM EGA full compatible                 |  |  |  |

| _             | ON         | PRT port used both for input and output |  |  |  |

| 2             | OFF        | PRT port only for output                |  |  |  |

|               | ON         | Communications port as CH2              |  |  |  |

| 3 OFF         |            | Communications port as CH1              |  |  |  |

| ON            |            | Double font in plasma for TEXT          |  |  |  |

| 4             | OFF        | Single font in plasma for TEXT          |  |  |  |

| F             | ON         | Disable CRTC for EXT.CRTC               |  |  |  |

| 5             | OFF        | Enable internal CRTC (normal)           |  |  |  |

|               | ON         | North European Font to display          |  |  |  |

| 6             | OFF        | Other Fonts (Normal)                    |  |  |  |

| 7 to 10       | (Defined a | s follows)                              |  |  |  |

### TABLE 1-1 DIP Switch Functions

| Monitor in use                                                        | 7   | 8   | 9   | 10  |

|-----------------------------------------------------------------------|-----|-----|-----|-----|

| Monochrome                                                            |     | OFF | OFF | OFF |

| Standard RGB<br>(40 column mode is default)                           | ON  | OFF | OFF | ON  |

| Standard RGB<br>(80 column mode is default)                           |     | OFF | OFF | ON  |

| Enhanced RGB<br>(200 line or emulation of standard RGB is<br>default) |     | ON  | ON  | OFF |

| Enhanced RGB<br>(350 line, true enhanced operation is default)        | OFF | ON  | ON  | OFF |

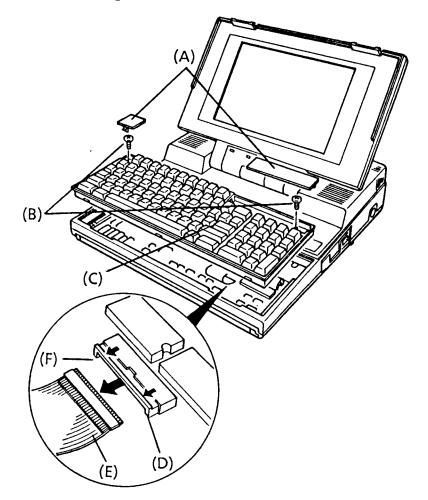

## 1.2.2 Jumper straps

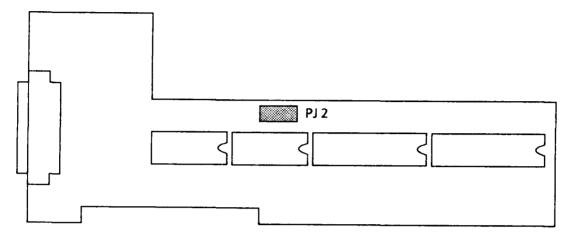

The system has six jumper straps (PJ 2) which are located on the keyboard control PCB.

Usually the six jumper straps are all open.

The following figure shows location of the jumper straps.

FIGURE 1-2 Jumper Strap Locations

The following table shows function of the jumper straps.

|       | Name                               | Function      |                                                                                                 |  |

|-------|------------------------------------|---------------|-------------------------------------------------------------------------------------------------|--|

| 1-2   | Not used                           |               |                                                                                                 |  |

| 3-4   | 2HD FDD type                       |               | 1.6 Mbytes<br>2.0 Mbytes                                                                        |  |

| 5-6   | Internal FDD numbers               | Open<br>Short | One FDD<br>Two FDD's                                                                            |  |

| 7-8   | FDD type                           | Open<br>Short | 2DD<br>2HD (1.6 Mbytes/2.0 Mbytes)                                                              |  |

| 9-10  | Standard memory size               | Open<br>Short | 640 kbytes<br>512 kbytes                                                                        |  |

| 11-12 | Used 3MB memory card mode (Option) |               | Used as the extended memory and<br>the expanded memory.<br>Used as the only expanded<br>memory. |  |

TABLE 1-2 Jumper Strap Functions

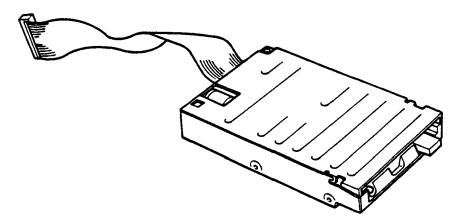

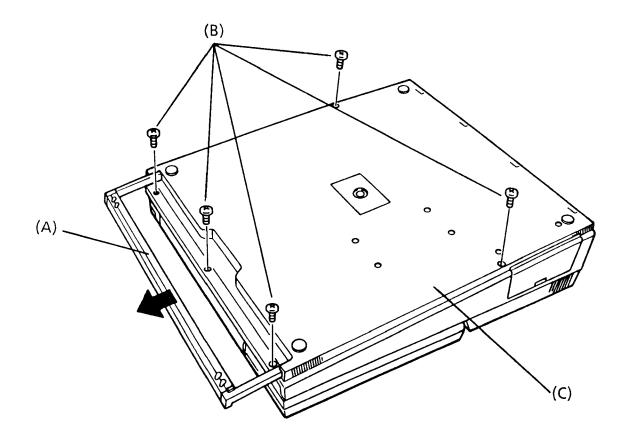

# 1.3 3.5-INCH FLOPPY DISK DRIVE

The floppy disk drive (FDD) used in the T3200 is high performance, high reliable, slim sized FDD for 3.5-inch floppy disks with recording capacity of 720 kbytes (formatted) in double-sided, double density and 135 tracks per inch operation. The specifications are as following table.

FIGURE 1-3 3.5-inch FDD

TABLE 1-3 3.5-inch Floppy Disk Drive Specifications

| ltem                                      | Specifications                         |

|-------------------------------------------|----------------------------------------|

| Storage Capacity (kilobytes)              | 1000 (unformatted)<br>720 (formatted)  |

| Number of Heads                           | 2                                      |

| Number of Track per Side                  | 80                                     |

| Track to Track Access (milliseconds)      | 3                                      |

| Head Settling Time (milliseconds)         | 15                                     |

| Track Density (tracks per inch)           | 135                                    |

| Motor Start-up Time (milliseconds)        | 500                                    |

| Data Transfer Rate (kilobits per second)  | 250                                    |

| Rotational Speed (revolutions per minute) | 300                                    |

| Recording Method                          | MFM (Modified frequency<br>modulation) |

## 1.4 3.5-INCH HARD DISK DRIVE

The hard disk drive (HDD) is random access storage, having recording capacity of 40 Mbytes (formatted). This is equipped with the storage media of non-removable 3.5-inch magnetic disks and mini-winchester type magnetic heads. The specifications are as following table.

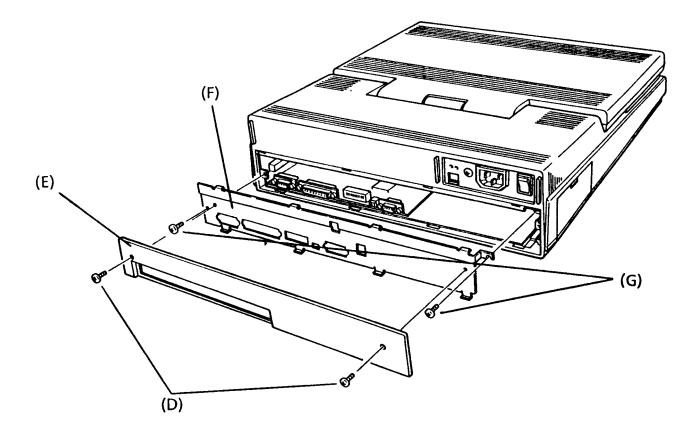

FIGURE 1-4 3.5-inch Hard Disk Drive

TABLE 1-4 3.5-inch Hard Disk Drive Specifications

| ltem                                 | Specifications                      |                                          |  |  |

|--------------------------------------|-------------------------------------|------------------------------------------|--|--|

| Storage Capacity (megabytes)         |                                     | 51.24 (unformatted)<br>40.30 (formatted) |  |  |

| Number of Heads                      |                                     | 8                                        |  |  |

| Number of Cylinders                  | 615                                 |                                          |  |  |

| Number of Tracks (tracks per cy      | ylinder)                            | 8                                        |  |  |

| Access Time (milliseconds)           | (minimum)<br>(average)<br>(maximum) | 8<br>38<br>85                            |  |  |

| Recording Density (bits per inc      | h)                                  | 14845                                    |  |  |

| Track Density (tracks per inch)      | 834                                 |                                          |  |  |

| <b>Rotational Speed (revolutions</b> | 3600                                |                                          |  |  |

| Recording Method                     |                                     | MFM (Modefied Frequency<br>Modulation)   |  |  |

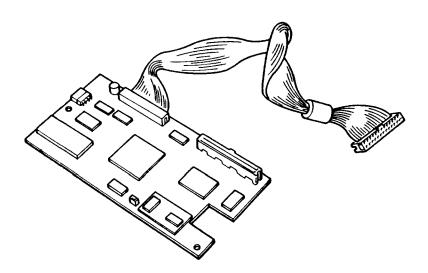

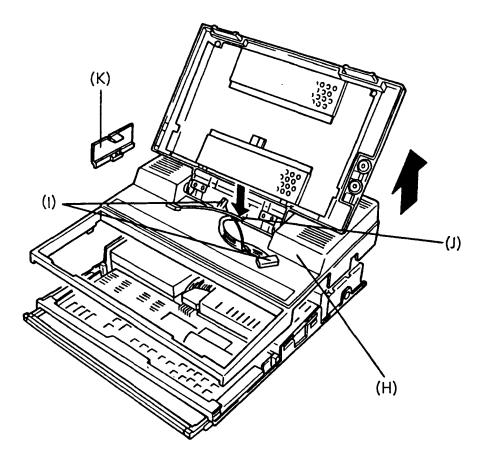

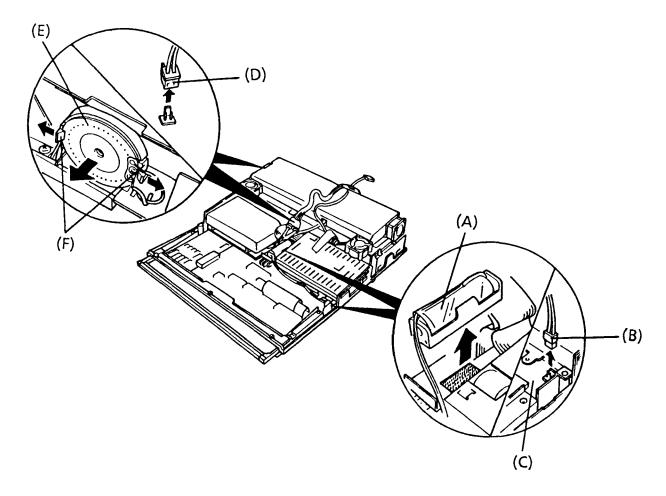

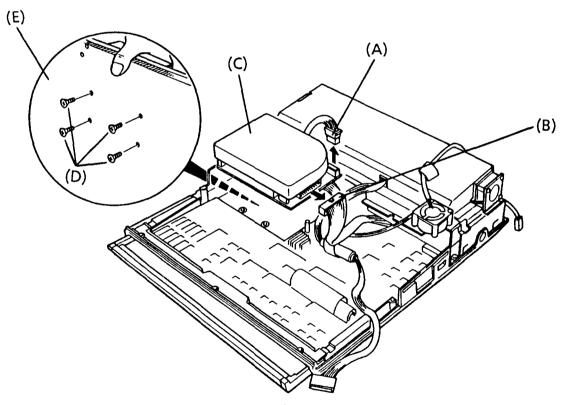

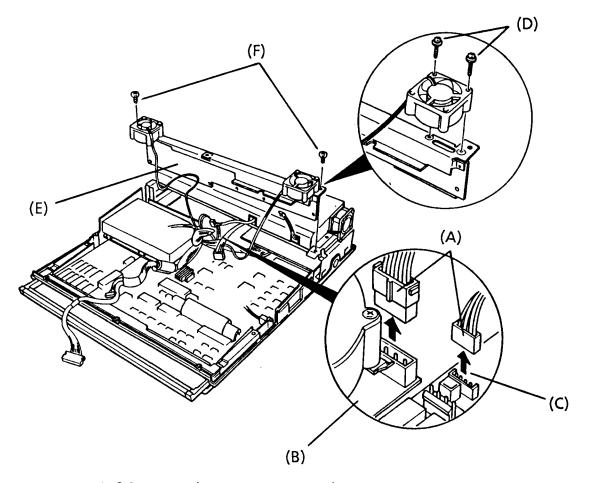

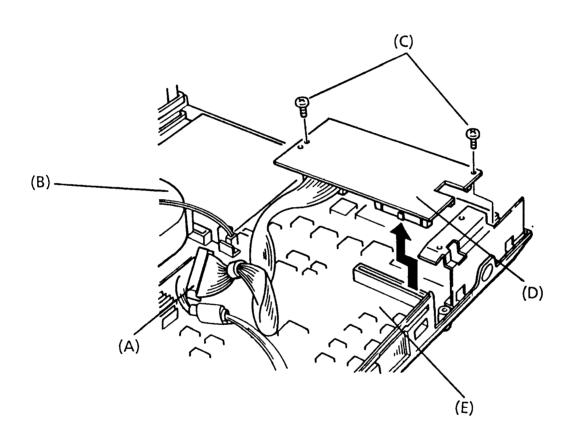

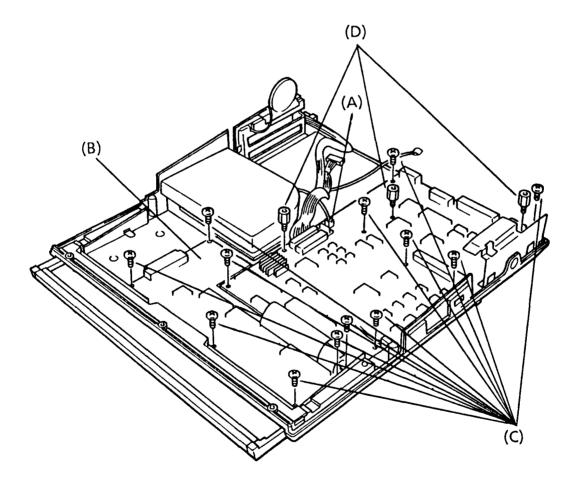

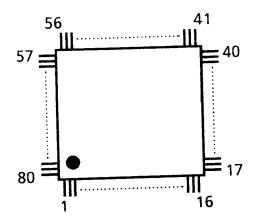

## 1.5 HARD DISK CONTROL PCB

Hard disk control PCB (HDC) is accompanied by hard disk drive (HDD) and connects to the system PCB through a cable. This HDC can interface the HDD to the system PCB. The specifications are as following table.

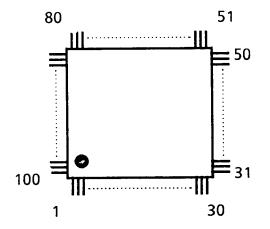

FIGURE 1-5 Hard Disk Control PCB

TABLE 1-5 Hard Disk Control PCB Specifications

| ltem                                             | Specifications                         |  |  |

|--------------------------------------------------|----------------------------------------|--|--|

| Encoding method                                  | MFM (Modefied Frequency<br>Modulation) |  |  |

| Data Transfer Rate (megabits per second) maximum | 5                                      |  |  |

| Write Precompensation time (nanoseconds)         | 12                                     |  |  |

| Sectoring                                        | Soft                                   |  |  |

The Hard disk control PCB has jumper straps which are PJ 3, PJ 4 and PJ 5. Functions of the jumper straps are as follows.

(1) PJ 3 Not used.

(2) PJ 4 This jumper straps select recording method of the hard disk control PCB. The following table shows function.

TABLE 1-6 PJ 4 Jumper Strap Functions

| No.        | Status        | Function   |

|------------|---------------|------------|

| 1-2<br>3-4 | Short<br>Open | MFM method |

(3) PJ 5

This jumper straps select the delay time of the hard disk control PCB. Usually delay time is selected as 20 ns. The following table shows function of the jumper straps.

TABLE 1-7 PJ 5 Jumper Strap Functions

| No.  | Delay time select |  |  |  |

|------|-------------------|--|--|--|

| 1-2  | 10 ns             |  |  |  |

| 3-4  | 15 ns             |  |  |  |

| 5-6  | 20 ns             |  |  |  |

| 7-8  | 25 ns             |  |  |  |

| 9-10 | 30 ns             |  |  |  |

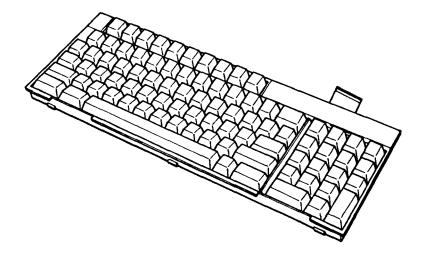

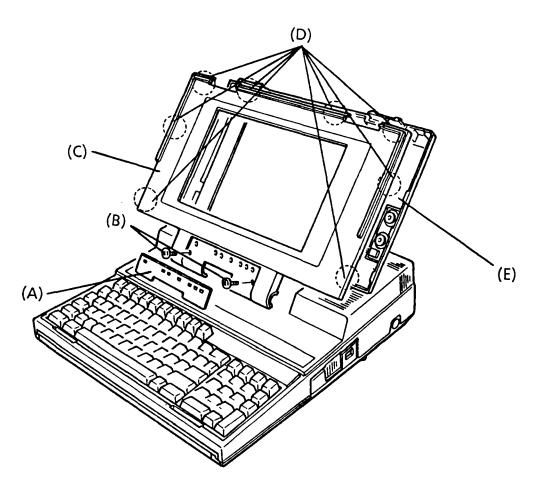

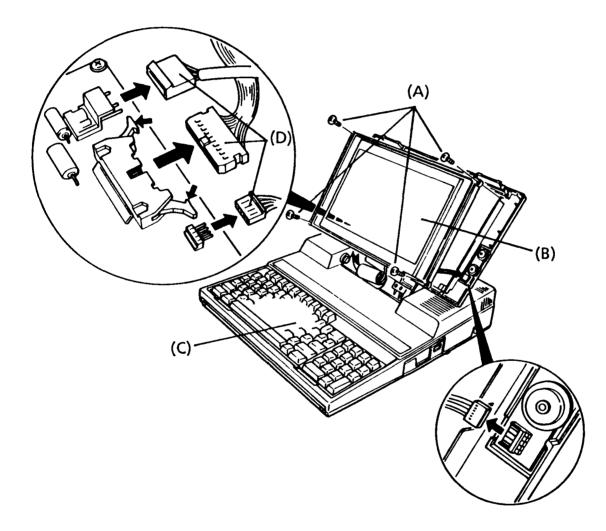

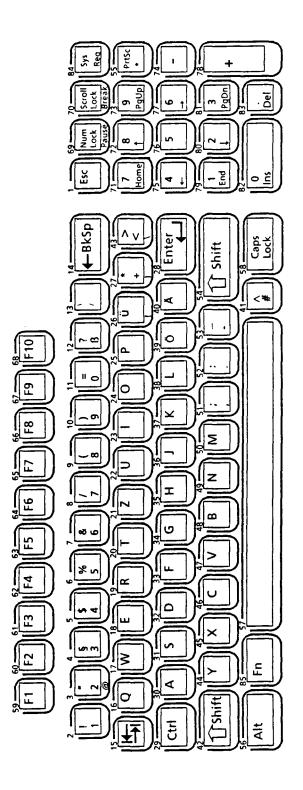

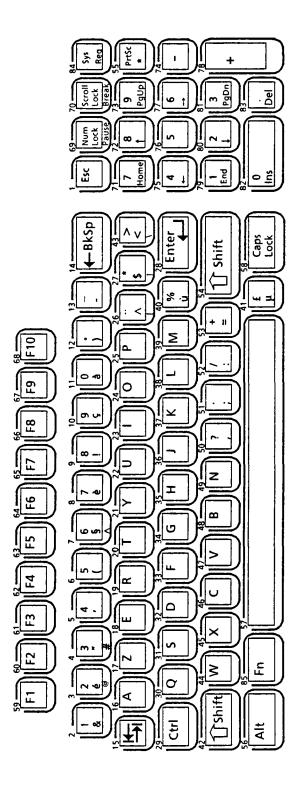

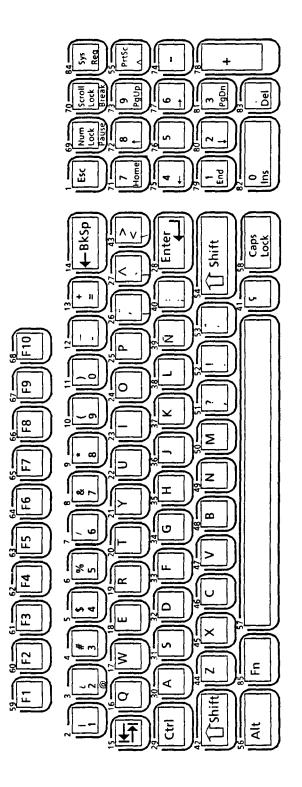

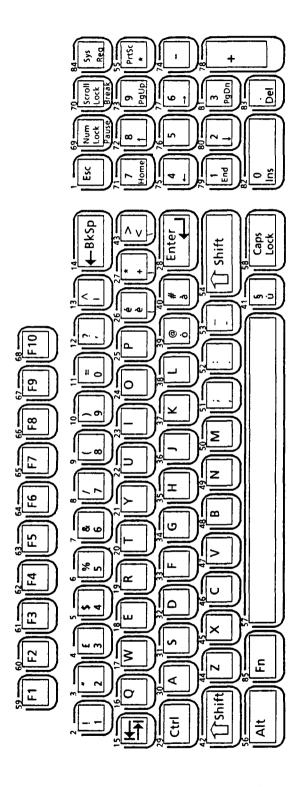

# 1.6 KEYBOARD

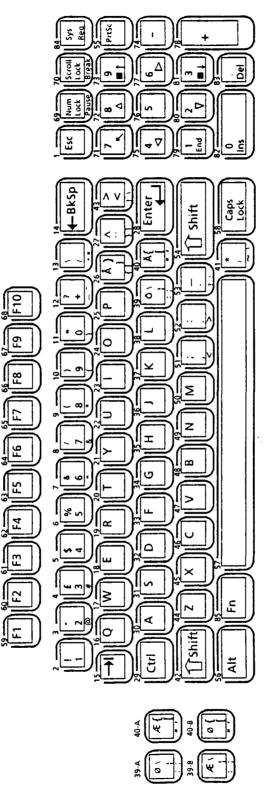

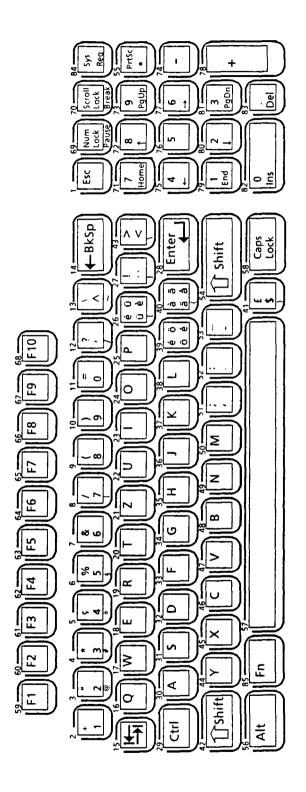

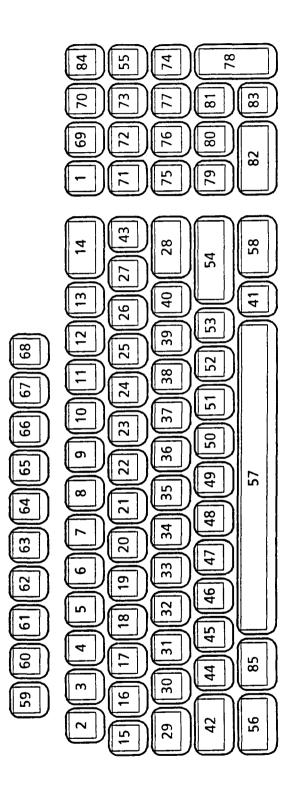

The keyboard is mounted on the system and has 85 keys. These consist of 54 standard keys, 10 function keys, 17 cursor keys, 14 functional keypads, and Fn key.

The keyboard is just a key matrix built up by the above keys. The keyboard is connected to the keyboard controller on the system PCB through a 22-pin flat cable.

FIGURE 1-6 Keyboard

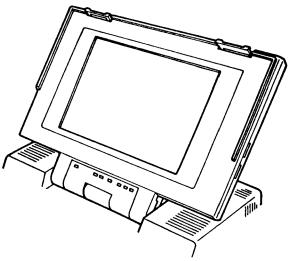

### 1.7 PLASMA DISPLAY

The plasma display is a graphics type display unit composed of the display panel and driver circuits. This receives vertical and horizontal sync signals, four bit data signals, and shift clock for data transmission. All these signals are TTL level compatible. The specifications are as following table.

The plasma display has 4-level of gray display. The plasma display be adjusted by contrast/brightness control volume.

FIGURE 1-7 Plasma Display

TABLE 1-8 Plasma Display Specifications

| ltem               | Specification                                            |

|--------------------|----------------------------------------------------------|

| Dot Number (dots)  | 720 x 400                                                |

| Dot Dimension (mm) | 0.18 (V) x 0.16 (H)                                      |

| Dot Pitch (mm)     | 0.36 (V) x 0.30 (H)                                      |

| Display Area (mm)  | 144 (V) x 216 (H)                                        |

| Contrast           | 1:10                                                     |

| Color              | Neon - orange                                            |

| Power Requirement  | + 5V ±0.5V, 0.6A<br>+ 205 ±5V, 170mA<br>+ 5V ±0.5V, 60mA |

| MTBF               | 20000 hours                                              |

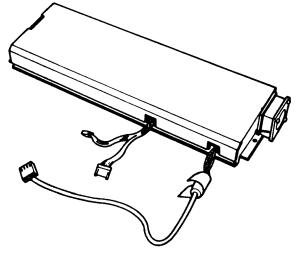

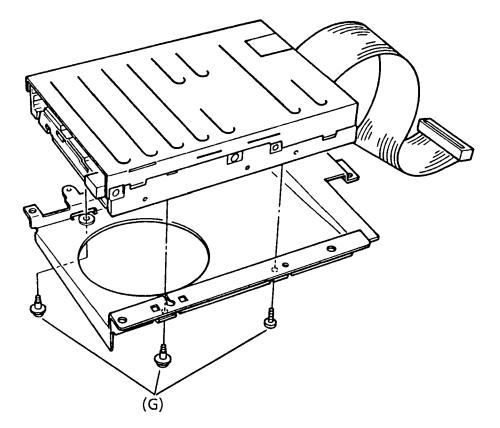

### 1.8 POWER SUPPLY UNIT

The power supply unit supplies dc 5, 12, -12 and 205 volts to all the components in the system. The power supply unit is housed in the system and is designed to support the following:

- System PCB

3.5-inch Floppy disk drive

- 3) 3.5-inch Hard disk drive

- 4) Hard disk control PCB

- 5) Keyboard unit

- 6) Plasma display

- 7) Option PCB's

The power supply unit includes the input line filter, line fuse, cooling fan, power conversion circuitry and connectors. Input rating is as follows.

AC 100, 115/220, 240 Volts, 60W (100W max.)

Output rating is as following table.

FIGURE 1-8 Power Supply Unit

TABLE 1-9 Power Supply Unit Output Rating

| FUNCTION       | DC VOLTAGE | REGULATION<br>TOLERANCE | MAX.<br>CURRENT |

|----------------|------------|-------------------------|-----------------|

| SYSTEM PCB     | 5 V        | ±5%                     | 6.5 A           |

| SYSTEM PCB     | 12 V       | ± 5 %                   | 2.6 A           |

| SYSTEM PCB     | -12 V      | + 10 %, - 20 %          | 0.3 A           |

| PLASMA DISPLAY | 205 V      | 200 to 210 V            | 170 mA          |

| PLASMA DISPLAY | 5 V        | ± 10 %                  | 60 mA           |

### 2.1 GENERAL

These problem isolation procedures are used to isolate defective FRUs (field replaceable units) to be replaced. FRUs consist of the following:

- 1. Power supply unit

- 2. System PCB

- 3. FDD

- 4. HDD and HDC

- 5. Keyboard

- 6. Plasma display

See PART 4 for detailed replacement procedures instructions. Test program operations are described in PART 3.

The following items are necessary for carrying out the problem isolation procedures.

- 1. T3200 Diagnostics disk

- 2. Flatbladed screwdriver

- 3. Work disk (for FDD testing)

- 4. Cleaning disk kit (for FDD testing)

- 5. Multimeter

- 6. Printer port LED

The problem isolation flowchart described in part 2.2 can be used to determine the necessary isolation procedures to be followed when there is a problem with the T3200.

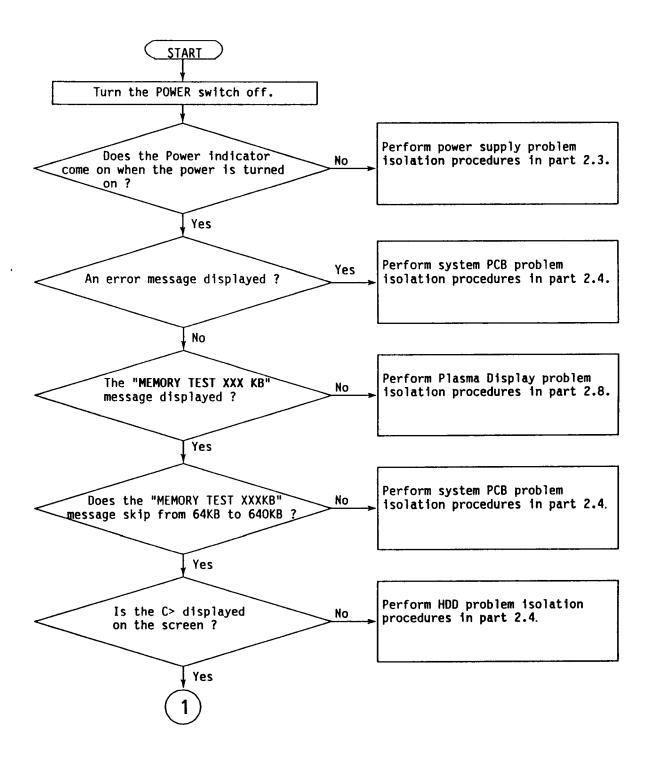

### 2.2 PROBLEM ISOLATION FLOWCHART

This flowchart is used as a guide for determining which FRU is defective. Please confirm the following before performing the flowchart procedures.

No disk is in the FDD.

All optional equipment is disconnected.

See next page.

FIGURE 2-1 Problem Isolation Flowchart

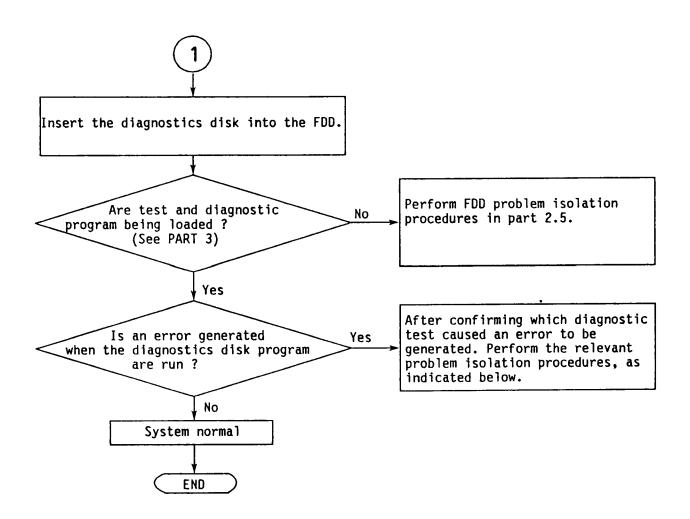

- 1. If an error is generated on the system test, memory test, display test and real timer test, go to system PCB isolation procedures in part 2.4.

- 2. If an error is generated on the hard disk test, go to HDD isolation procedures in part 2.6.

- 3. If an error is generated on the keyboard test, go to keyboard isolation procedures in part 2.8.

- 4. If an error is generated on the floppy disk test, go to FDD isolation procedures in part 2.5.

# 2.3 POWER SUPPLY UNIT ISOLATION PROCEDURES

This section describes how to determine whether the power supply PCB is defective or not. The procedures below are outlined in the following pages. They should be performed in the order indicated.

- PROCEDURE 1: Power Indicator Check

- PROCEDURE 2: Connector Check

- PROCEDURE 3: Output Voltage Check

- PROCEDURE 4: Power Supply Unit Voltage Adjustment

- PROCEDURE 5: Power Supply Unit Replacement

.

### Power Indicator Check

- 1. Turn the POWER switch on.

- 2. If the POWER indicator lights, go to PROCEDURE 3. If the indicator doesn't light, replace the ac cord; if it lights, the previous ac cord was defective. If the indicator doesn't light yet, go to PROCEDURE 2.

FIGURE 2-2 POWER Indicator Check

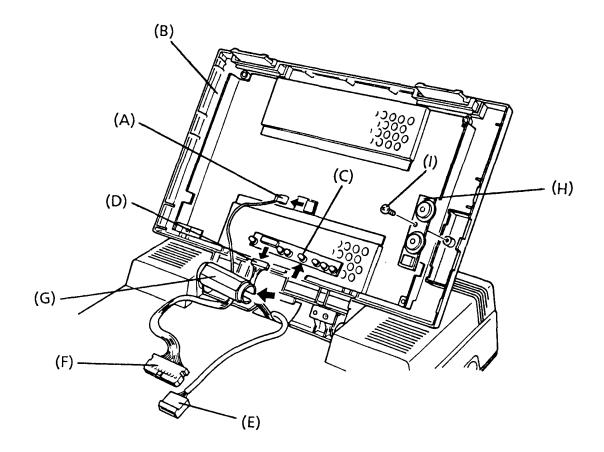

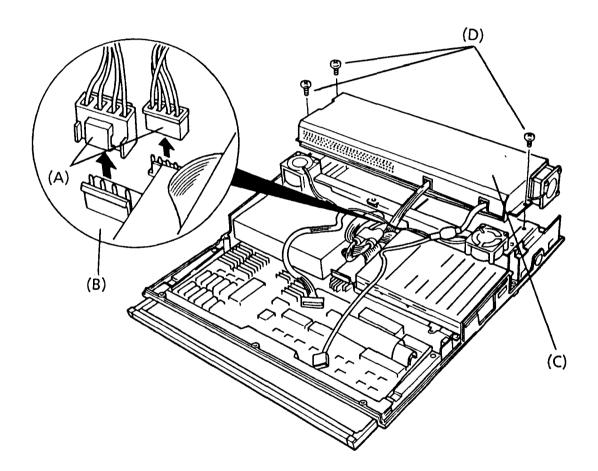

Connector Check

- 1. Turn the POWER switch off and unplug the ac cord.

- 2. Remove the top cover. (Refer to part 4.2.)

- 3. If the two system PCB connectors (PJ 7 and 8) are connected properly, go to PROCEDURE 3; if they are not connected properly, reconnect them.

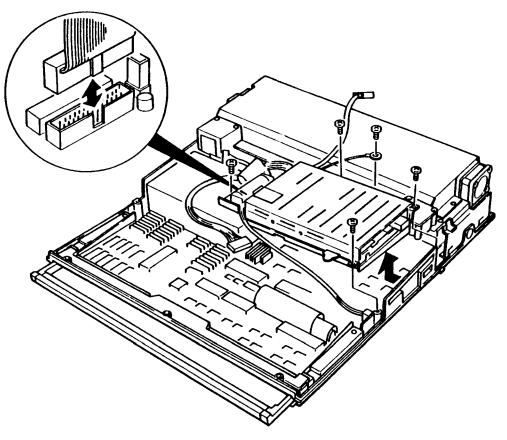

FIGURE 2-3 Power Supply Unit Connectors

#### Output Voltage Check

- 1. Disconnect the three power cables (for plasma display and system PCB) from the system PCB.

- 2. Plug the ac cord, then turn the POWER switch on.

- 3. Use a multimeter to confirm that the output voltages for the three power supply PCB connectors conform to the values given in the following table.

- 4. If the voltages conform to the values given in the table, the power supply PCB is normal. System PCB is probably defective, go to system PCB isolation procedures in part 2.4.

- 5. If the voltages do not conform to those given in the table, go to PROCEDURE 4.

| CONNECTOR | PIN NUMBER |        | VOLTAGE (Vdc) |        |        |

|-----------|------------|--------|---------------|--------|--------|

| CONNECTOR | + lead     | - lead | Normal        | Min    | Max    |

| PJ 003    | 1          | 3,4    | + 5           | + 4.75 | + 5.25 |

|           | 2          | 3,4    | + 5           | + 4.75 | + 5.25 |

| PJ 004    | 1          | 2,4    | + 12          | + 11.4 | + 12.6 |

|           | 3          | 2,4    | - 12          | - 13.2 | - 9.6  |

| PJ 005    | 1          | 2      | + 205         | + 200  | + 210  |

|           | 3          | 2      | + 5           | + 4.5  | + 5.5  |

TABLE 2-1 Power Supply Unit Output Voltages

Power Supply Unit Voltage Adjustment

- 1. Turn the POWER switch off and unplug the ac cord.

- 2. Remove the power supply unit. (Refer to part 4.9.)

- 3. Remove the power supply unit cover from the power supply unit.

- 4. Set the dummy load resister (1.3 kiloohm, 35 W) to the plasma display power connector (1-pin to 2-pin).

- 5. Plug the ac cord to the power supply unit, then turn the POWER switch on.

- 6. Use a multimeter to confirm that the output voltages for the plasma display power connector conform to the volues given in the following table.

TABLE 2-2 VR1 Adjustment

| CONNECTOR | PIN NU | JMBER  | VOLTAGE (Vdc) |       |  |

|-----------|--------|--------|---------------|-------|--|

| CONNECTOR | + lead | - lead | Min           | Мах   |  |

| PJ 005    | 1      | 2      | + 201         | + 202 |  |

- 7. If the voltage does not conform to that given in the table, after turn the VR2 to the right, then adjust the VR1 on the power supply PCB by Phillips screwdriver.

- 8. Turn the POWER switch off, then remove the dummy load resister (1.3 kiloohm, 35 W).

- 9. Set the dummy load resister (21 kiloohm, 2.5 W) to the prasma display power connector (1-pin to 2-pin).

- 10. Adjust the VR2 on the system PCB that the output voltages for the plasma display power connector conform to the values given in the following table.

| TABLE 2-3 VR2 | Adjustment |

|---------------|------------|

|---------------|------------|

| CONNECTOR | PIN NU | IMBER  | VOLTAGE (Vdc) |       |  |

|-----------|--------|--------|---------------|-------|--|

| CONNECTOR | + lead | - lead | Min           | Max   |  |

| PJ 005    | 1      | 2      | + 208         | + 209 |  |

Power Supply Unit Replacement

- 1. Turn the POWER switch off and unplug the ac cord.

- 2. Replace the power supply unit. (Refer to part 4.9.)

- 3. If normal operation is restored after replacing the power supply unit, the previous power supply unit was defective.

- 4. If normal operation is not restored, another FRU is probably defective. The defective unit must be isolated and replaced.

### 2.4 SYSTEM PCB ISOLATION PROCEDURES

This section describes how to determine whether the system PCB is defective or not. The procedures below are outlined in the following pages. They should be performed in the order indicated.

PROCEDURE 1: Message Check

PROCEDURE 2: Printer Port LED Check

PROCEDURE 3: Test Program Execution

PROCEDURE 4: System PCB Replacement

**NOTE:** Before carrying out any of these procedures, make sure that there is not a floppy disk in the FDD.

Message Check

- 1. Turn the POWER switch on.

- 2. If the system is loaded, go to PROCEDURE 3.

- If the following message is displayed on the screen, press the Fl key. Execute the setup. (Refer to OWNER'S MANUAL in PART 6.)

\*\*\* Error in CMOS. Bad battery \*\*\* Check system Then. press [F1] key .....

\*\*\* Error in CMOS. Bad check sum \*\*\* Check system Then. press [F1] key .....

\*\* Error in CMOS. Bad configuration \*\* Check system Then. press [F1] key .....

\*\*\* Error in CMOS. Bad memory size \*\*\* Check system Then. press [F1] key .....

\*\* Error in CMOS. Bad time function \*\*

Check system Then. press [F1] key .....

4. If the following message is displayed on the screen, go to HDD isolation procedures in part 2.6.

\*\* HDD Load error or Bad system disk \*\* Insert system disk in drive Press any key when ready .....

5. If none of the messages are displayed and you have a printer port LED, go to PROCEDURE 3. If none the messages are displayed and you don't have a printer port LED, go to PROCEDURE 2. Beep Sound Check

- 1. Turn the POWER switch off.

- 2. Turn the POWER switch on.

- 3. If the system occurs an error, the system informs you of an error code with the beep sound. (That is the bit information of DL register.) The system repeats the buzzer message three times. A hexadecimal number is configured by the combination of two groups of the beep sounds, each of which is composed of either short sounds or long sounds. The status of an error code is as following table.

- 4. If the error code conforms to the values given in the table, go to PROCEDURE 5.

- 5. If the error code doesn't conform to the values given in the table, another FRU is probably defective.

TABLE 2-4 Beep Sound Error Code

| 0H |            |      |   |          |       |       |   |

|----|------------|------|---|----------|-------|-------|---|

| 1H |            |      |   |          |       |       |   |

| 2H | <br>—      |      |   |          |       |       |   |

| 3H | <br>—      |      |   |          |       |       |   |

| 4H | <br>—      | <br> |   |          |       |       |   |

| 5H | <br>       | <br> |   |          |       |       |   |

| 6H | <br>       | <br> | - |          |       |       |   |

| 7H | <br>       | <br> |   |          |       |       |   |

| 8H | <br>       | <br> |   |          |       |       |   |

| 9Н | <br>       | <br> |   |          |       |       |   |

| AH | <br>       | <br> |   |          |       |       |   |

| вн | <br>       | <br> |   |          | <br>  |       |   |

| СН | <br>······ | <br> |   |          | <br>— |       |   |

| DH | <br>       | <br> |   | <u> </u> | <br>  | <br>— |   |

| EH | <br>       | <br> |   |          | <br>— | <br>  | — |

| FH | <br>       | <br> |   |          | <br>  | <br>  |   |

#### Printer Port LED Check

- 1. Turn the POWER switch off.

- 2. Plug the printer port LED into the PRT/FDD connector on the back of the unit.

- 3. Turn the POWER switch on while watching the printer port LED. The printer port LED will light at the same time that the POWER switch is turned on.

- 4. Read the final LED status as a hexadecimal value from left to right.

- 5. If the final LED status matches any of the error code values in the table 2-6 (See the next page.), go to PROCEDURE 5.

- 6. If the final LED status is **19H**, go to PROCEDURE 4 and continue.

| Status | Messages                                                  |

|--------|-----------------------------------------------------------|

| 01 (H) | Initial setup of LSI start                                |

| 02 (H) | Initial setup of RTC end                                  |

| 03 (H) | Initial setup of PIT end                                  |

| 04 (H) | Initial setup of DMAC(#1) end                             |

| 05 (H) | Initial setup of DMAC(#2) end                             |

| 06 (H) | Initial setup of PIC (#1) end                             |

| 07 (H) | Initial setup of PIC (#2) end                             |

| 08 (H) | Initial setup of DMA page register end                    |

| 09 (H) | Initial setup of KB controller end                        |

| 0A (H) | Initial setup of memory (0 - 64 KB) end                   |

| 0B (H) | Initial setup of memory (64 - 640 KB) end                 |

| 0C (H) | Initial setup of memory (more than 1 MB) Protect mode end |

| 0D (H) | Initial setup of memory (more than 1 MB) Real mode end    |

| 0E (H) | Check a checksum of CMOS end                              |

| 0F (H) | Check classification of CRT end                           |

| 10 (H) | Check item of CMOS end                                    |

| 11 (H) | Initial setup of CRT end                                  |

| 12 (H) | Initial setup of keyboard end                             |

| 13 (H) | Initial setup of Timer end                                |

| 14 (H) | Initial setup of FDD end                                  |

| 15 (H) | Initial setup of HDD end                                  |

| 16 (H) | Initial setup of option ROM end                           |

| 17 (H) | Initial setup of printer end                              |

| 18 (H) | Initial setup of RS232C end                               |

| 19 (H) | Prepare the boot end                                      |

TABLE 2-5 Printer Port LED Normal Status

# TABLE 2-6 Printer Port LED Error Status

| Status          | Error Messages                     | Process |  |

|-----------------|------------------------------------|---------|--|

| 81 (H)          | Exception (size proc)              | HALT    |  |

| 82 (H)          | Failed PM (size proc)              | HALT    |  |

| 83 (H)          | ADR 20 failed (size proc)          | HALT    |  |

| 84 (H)          | KBC Self test error                | HALT    |  |

| 85 (H)          | KBC not ready I (KBC init)         | HALT    |  |

| 86 (H)          | KBC not ready_O (KBC init)         | HALT    |  |

| 87 (H)          | KBC not ready_ I (size ret)        | HALT    |  |

| 8 <b>8 (</b> H) | KBC not ready [ (ex. ret size)     | HALT    |  |

| 89 (H)          | KBC not ready   (mono set)         | HALT    |  |

| 8A (H)          | KBC not ready I (KB init)          | HALT    |  |

| 8B (H)          | KBC not ready I (PRT init)         | HALT    |  |

| 8C (H)          | KBC not ready O (PRT init)         | HALT    |  |

| 91 (H)          | PE = 1 (start)                     | HALT    |  |

| 92 (H)          | PE = 0 (size proc)                 | HALT    |  |

| 93 (H)          | PE = 0 (mem test)                  | HALT    |  |

| 94 (H)          | ROM check sum error                | HALT    |  |

| A1 (H)          | RTC data bus error                 | HALT    |  |

| A2 (H)          | RTC int. error                     | HALT    |  |

| A3 (H)          | RTC clock error                    | HALT    |  |

| A4 (H)          | PIT data bus error                 | HALT    |  |

| A5 (H)          | PIT ch.2 output error              | HALT    |  |

| A6 (H)          | PIT clock error                    | HALT    |  |

| A7 (H)          | PIT ch.1 output error              | HALT    |  |

| A8 (H)          | PIT ch.0 output error              | HALT    |  |

| A9 (H)          | DMAC #1 data bus error             | HALT    |  |

| AA (H)          | DMAC #2 data bus error             | HALT    |  |

| AB (H)          | PIC #1 data bus error              | HALT    |  |

| AC (H)          | PIC #1 data bus error              | HALT    |  |

| AD (H)          | PIC #2 data bus error              | HALT    |  |

| AE (H)          | PIC #2 data bus error              | HALT    |  |

| AF (H)          | MAPPER data bus error              | HALT    |  |

| B1 (H)          | MAPPER address error               | HALT    |  |

| 82 (H)          | Word/byte error (I/O)              | HALT    |  |

| B3 (H)          | Exception (mem test)               | HALT    |  |

| B4 (H)          | Failed PM (mem test)               | HALT    |  |

| B5 (H)          | KBC not ready_l (ex. ret mem test) | HALT    |  |

| B6 (H)          | ADR 20 failed (mem test)           | HALT    |  |

| B7 (H)          | KBC NOT ready I (mem test)         | HALT    |  |

| Status | Error Messages                       | Process |

|--------|--------------------------------------|---------|

| B8 (H) | KBC not ready_O (FDD int)            | HALT    |

| C1 (H) | Mem (base 64KB) data bus error       | HALT    |

| C2 (H) | Mem (base 64KB) word/byte error      | HALT    |

| C3 (H) | Mem (base 64KB) fixed data error     | HALT    |

| C4 (H) | Mem (base 64KB) address error        | HALT    |

| C8 (H) | Mem (base 64KB) parity circuit error | HALT    |

| C9 (H) | Mem (base 64KB) parity circuit error | HALT    |

| CA (H) | Mem (base 64KB) parity circuit error | HALT    |

| CB (H) | Mem (base 64KB) parity circuit error | HALT    |

| CC (H) | Mem (base 64KB) parity circuit error | HALT    |

| D0 (H) |                                      |         |

| D1 (H) | Mem (64 KB - ) data bus error        | HALT    |

| D2 (H) | Mem (64 KB - ) word/byte error       | HALT    |

| D3 (H) | Mem (64 KB - ) fixed error           | HALT    |

| D4 (H) | Mem (64 KB - ) address error         | HALT    |

| D5 (H) | Mem address error                    | HALT    |

| D8 (H) | Mem (64 KB - ) parity circuit error  | HALT    |

| D9 (H) | Mem (64 KB - ) parity circuit error  | HALT    |

| DA (H) | Mem (64 KB - ) parity circuit error  | HALT    |

| DB (H) | Mem (64 KB - ) parity circuit error  | HALT    |

| DC (H) | Mem (64 KB - ) parity circuit error  | HALT    |

| E1 (H) | Video RAM error (mono)               | HALT    |

| E2 (H) | Video RAM error (plasma/color)       | HALT    |

| E3 (H) | Video RAM error (plasma)             | HALT    |

| E4 (H) | CRTC error (mono)                    | HALT    |

| E5 (H) | CRTC error (plasma/color)            | HALT    |

| E6 (H) | FDC error                            | HALT    |

#### Test Program Execution

- 1. Execute the following test program. (See PART 3 TEST AND DIAGNOSTICS.)

- 1. System test

- 2. Memory test

- 3. Keyboard test

- 4. Display test

- 5. Floppy disk test

- 6. Hard disk test

- 7. Real timer test

- 2. If an error is generated on the system test, memory test, display test and real timer test, go to PROCEDURE 5.

- 3. If an error is generated on the floppy disk test, go to FDD isolation procedures in part 2.5.

- 4. If an error is generated on the hard disk test, go to HDD isolation procedures in part 2.6.

- 5. If an error is generated on the keyboard test, go to keyboard isolation procedures in part 2.7.

### System PCB Replacement

- 1. Replace the system PCB. (Refer to part 4.14)

- 2. If normal operation is restored after replacing the PCB, the previous PCB was defective.

- 3. If normal operation is not restored, another FRU is probably defective. The defective unit must be isolated and replaced.

# 2.5 FLOPPY DISK DRIVE ISOLATION PROCEDURES

This section describes how to determine whether the floppy disk drive is defective or not. The procedures below are outlined in the following pages. They should be performed in the order indicated.

PROCEDURE 1: Test and Diagnostic Program Loading Check

PROCEDURE 2: Message Check

PROCEDURE 3: Head Cleaning

PROCEDURE 4: FDD Test Execution

PROCEDURE 5: FDD Connector Check

PROCEDURE 6: New FDD connection

Test and Diagnostic Programs Loading Check

- 1. Turn the POWER switch off.

- 2. Insert the diagnostics disk into the FDD.

- 3. Turn the POWER switch on.

- 4. If loading occurs normally, go to PROCEDURE 3. (See PART 3 to determine if loading has occurred normally.)

- 5. If loading has not occurred normally, go to PROCEDURE 2.

Message Check

- When the diagnostics disk is inserted into the FDD and the POWER switch is turned on, message (a), message (b), message (c) or message (d) should appear.

- (a) **\*\*\*\*** FDD A in not installed **\*\*\*\***

- (b) Non-System disk or disk error Replace and press any key when ready

- \*\* FDD load error or Bad system disk \*\*(c) Insert system disk in drive Press any key when ready .....

- (d) \*\* HDD Load error or Bad system disk \*\*(d) Insert system disk in drivePress any key when ready ....

- 2. If (a) of the above message is displayed, confirm that the A-B-PRT switch is set to the PRT side. If it is not seted to the PRT side, set the PRT side; if it is seted to the PRT side, go to PROCEDURE 5.

- 3. If (b), (c) or (d) of the above messages is displayed, the contents of the floppy disk are damaged, or some other disk than the diagnostics disk has been inserted into the FDD. Change the diagnostics disk. If loading then occurs, go to PROCEDURE 4; if loading does not occur, go to PROCEDURE 3.

- 4. If none of the above messages appears, go to PROCEDURE 5.

Head Cleaning

- 1. Turn the POWER switch off.

- 2. Insert the cleaning disk to the FDD.

- 3. Turn the POWER switch on.

- 4. If normal operation is restored after cleaning the head, go to PROCEDURE 4.

- 5. If normal operation is not restored, go to PROCEDURE 5.

FDD Test Execution

- 1. Run the floppy disk test which is indicated in the Diagnostic Test Menu.

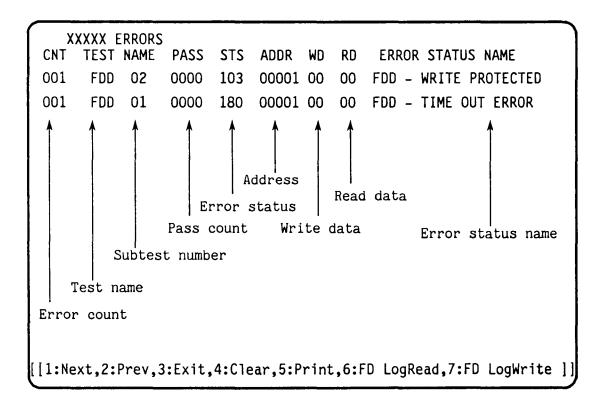

- 2. If an error is generated during the floppy disk test, an error code and status will be displayed as indicated in the following table. Follow the directions provided in the table.

- 3. If no error is generated, the FDD is normal.

| CODE | STATUS                            |

|------|-----------------------------------|

| 01   | Bad Command                       |

| 02   | Address Mark Not Found            |

| 03   | Write Protected                   |

| 04   | Recod Not Found                   |

| 06   | Media removed on dual attach card |

| 08   | DMA Overrun Error                 |

| 09   | DMA Boundary Error                |

| 10   | CRC Error                         |

| 20   | FDC Error                         |

| 40   | SEEK ERROR                        |

| 60   | FDD not drive                     |

| 80   | Time Out Error (Not Ready)        |

| EE   | Write buffer error                |

TABLE 2-7 FDD Error Status

FDD Connector Check

- 1. Turn the POWER switch off and disconnect the ac cord.

- 2. Remove the top cover. (Refer to part 4.2.)

- 3. If the FDD cable is connected to the system PCB securely, go to PROCEDURE 6.

- 4. If the above connections are not secure, reconnect them.

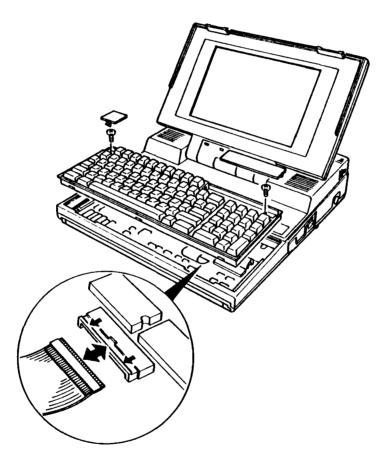

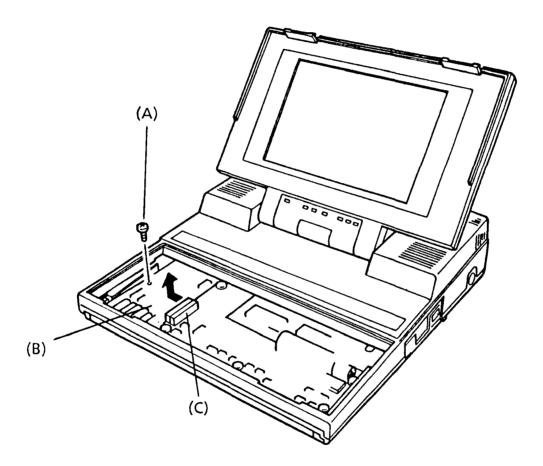

FIGURE 2-4 FDD Connector Check

New FDD Connection

- 1. Turn the POWER switch off.

- 2. Remove the FDD. (Refer to part 4.10.)

- 3. Connect the new FDD to the FDD connector, then other connectors too.

- 4. Turn the POWER switch on.

- 5. If normal operation is restored after connect the new FDD, the previous FDD was defective. Assemble the system.

- 6. If normal operation is not restored, system PCB is probably defective. Refer to part 2.4.

## 2.6 HARD DISK DRIVE ISOLATION PROCEDURES

This section describes how to determine whether the Hard Disk Drive is defective or not. The procedures below are outlined in the following pages. They should be performed in the order indicated.

PROCEDURE 1: HDD Indicator Check

PROCEDURE 2: Message Check

PROCEDURE 3: Format Execution

PROCEDURE 4: Hard Disk Test Execution

PROCEDURE 5: Connector Check

PROCEDURE 6: New HDC Connection

PROCEDURE 7: New HDD Connection

HDD Indicator Check

- 1. Turn the POWER switch off.

- 2. If there is a floppy disk in the FDD, take it out.

- 3. Turn the POWER switch on.

- 4. If the HDD indicator (Disk In Use Left) blinks briefly and goes out, go to PROCEDURE 2; if it continues blinking, go to PROCEDURE 4.

- 5. If the indicator does not light at all, go to PROCEDURE 5.

FIGURE 2-5 HDD Indicator Check

Message Check

- 1. If the system is loaded, go to PROCEDURE 4.

- 2. If the following message is displayed on the screen, go to PROCEDURE 3.

\*\* HDD Load error or Bad system disk \*\* Insert system disk in drive Press any key when ready ....

### Format Execution

- **CAUTION:** The contents of the hard disk will be erased when the FORMAT command is run. Before running the test, transfer the contents of the hard disk on the floppy disk. This can be done with the MS-DOS BACKUP command. (See the MS-DOS manual for details.)

- 1. Remove the diagnostics disk, and then insert the MS-DOS system disk to the FDD.

- 2. To set the partition of the hard disk, enter the FDISK command. (See the MS-DOS manual for details.)

- 3. To format the hard disk, enter the FORMAT command. (See the MS-DOS manual for details.)

- 4. If normal operation is restored, the HDD is normal.

- 5. If normal operation is not restored, go to PROCEDURE 6.

#### Hard Disk Test Execution

- CAUTION: The contents of the hard disk will be erased when the test program is run. Before running the test, transfer the contents of the hard disk on the floppy disk. This can be done with the MS-DOS BACKUP command. (See the MS-DOS manual for details.)

- 1. Insert the diagnostics disk into the FDD and load the test and diagnostic programs.

- 2. Run the hard disk test which is indicated in the diagnostics test menu.

- 3. If an error is generated during the hard disk test, an error code and status will be displayed as indicated in the following table. Go to PROCEDURE 6.

- 4. If no error is generated, the HDD is normal. Enter the MS-DOS FDISK command which will set the partition. Then enter the MS-DOS FORMAT command. (See the MS-DOS manual for details.)

| CODE | STATUS                         |

|------|--------------------------------|

| 01   | Bad command error              |

| 02   | Bad address mark               |

| 04   | Record not found               |

| 05   | HDC NOT RESET                  |

| 07   | Drive not initialize           |

| 09   | DMA Boundary error             |

| 0A   | Bad sector error               |

| OB   | Bad track error                |

| 10   | ECC error                      |

| 11   | ECC recover enable             |

| 20   | HDC error                      |

| 40   | Seek error                     |

| 80   | Time out error                 |

| AA   | Drive not ready                |

| BB   | Undefined                      |

| CC   | Write fault                    |

| EO   | Status error                   |

| FO   | Not sense error (HW.code = FF) |

#### TABLE 2-8 HDD Error Status

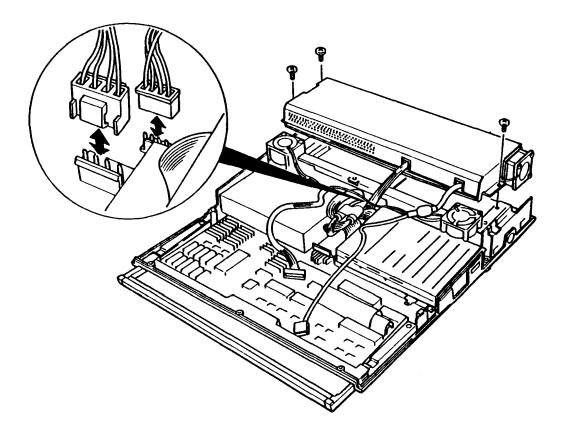

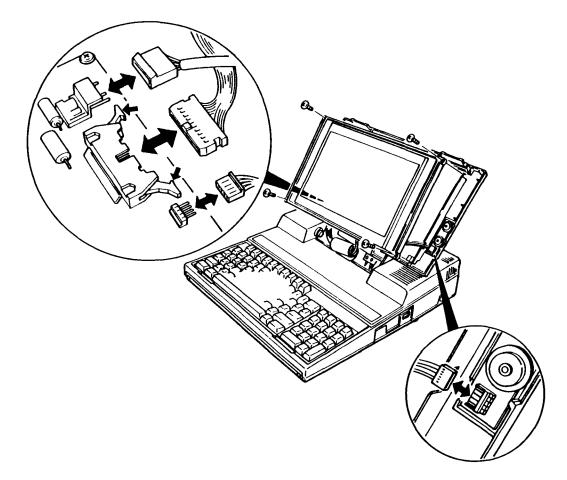

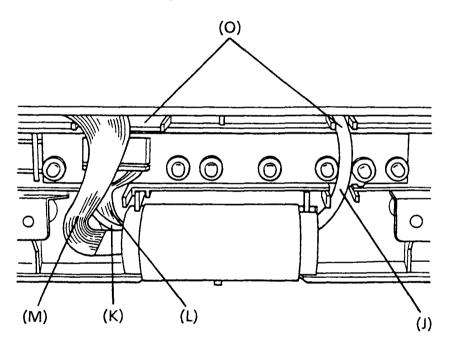

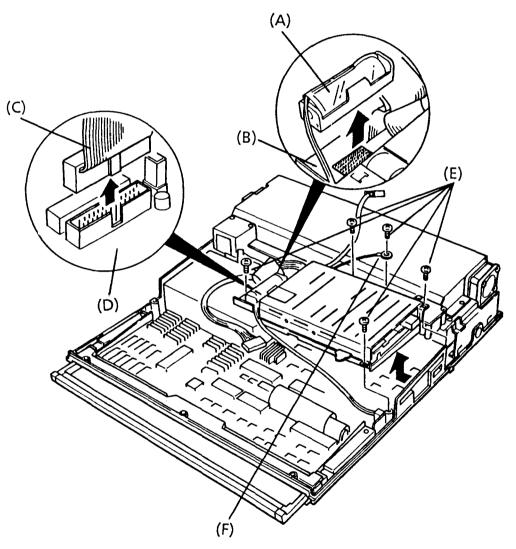

Connector Check

- 1. Turn the POWER switch off and disconnect the ac cord.

- 2. Remove the top cover. (Refer to part 4.2)

- J. If the HDD, HDC, and system PCB are connected securely, go to PROCEDURE 6.

- 4. If they are not connected securely, reconnect them.

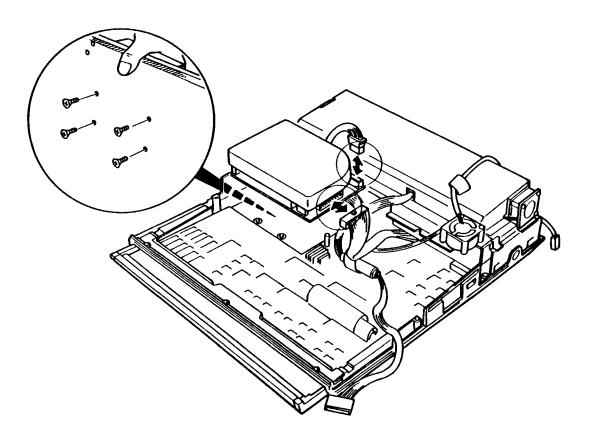

FIGURE 2-6 HDC and HDD Connector Check

New HDC Connection

- 1. Turn the POWER switch off and disconnect the ac cord.

- 2. Remove the HDC. (Refer to part 4.13.)

- 3. Connect the new HDC to the system PCB and HDD, then other connectors too.

- 4. If normal operation is restored, the previous HDC was defective. Assemble the system.

- 5. If normal operation is not restored, HDD is probably defective. Go to PROCEDURE 7.

New HDD Connection

- 1. Turn the POWER switch off.

- 2. Remove the HDD. (Refer to part 4.11.)

- 3. Connect the new HDD to the HDC, then other connectors too.

- 4. If normal operation is restored, the previous HDD was defective. Assemble the system.

- 5. If normal operation is not restored, system PCB is probably defective. System PCB is probably defective. Refer to part 2.4.

## 2.7 KEYBOARD ISOLATION PROCEDURES

This section describes how to determine whether the keyboard is defective or not. The procedures below are outlined in the following pages. They should be performed in the order indicated.

PROCEDURE 1: Input Check

PROCEDURE 2: Keyboard Test Execution

PROCEDURE 3: Connector Check

PROCEDURE 4: New Keyboared Connection

Input Check

- 1. Load either the diagnostics disk or the MS-DOS system disk.

- 2. When a prompt (A, B, C, etc.) appears on the screen, hit any of the white keys on the keyboard (any character or the space bar). If the character you hit appears on the screen, go to PROCEDURE 2.

- 3. If the character does not appear, go to PROCEDURE 3.

Toshiba Personal Computer MS-DOS Version 3.20 / (RXXXXX) (C) Copyright Toshiba Corporation 1983,1986 (C) Copyright Microsoft Corporation 1981,1986 Current date is XXX X-XX-19XX Enter new date (mm-dd-yy) : \_\_\_ Current time is X:XX:XX,XX Enter new time : \_\_\_ COMMAND Version 3.20 A> abcdefghijklmnopqrst.....

## Keyboard Test Execution

- 1. Insert the diagnostics disk into the FDD and load the test and diagnostics programs. (Refer to PART 3.)

- 2. Run the keyboard test which is indicated in the diagnostics test menu.

- 3. If an error is generated during the test, go to PROCEDURE 3.

- 4. If no error is generated during the test, the keyboard is normal.

Connector Check

- 1. Turn the POWER switch off and disconnect the ac cord.

- 2. Remove the top cover. (Refer to part 4.2)

- 3. Lift the keyboard up and check that the keyboard cable is connected securely to the system PCB. If it is connected securely, go to PROCEDURE 4.

- 4. If it is not connected securely, reconnect it.

FIGURE 2-7 Keyboard Connector Check

New Keyboard Connection

- 1. Turn the POWER switch off and unplug the ac cord.

- 2. Remove the keyboard unit. (Refer to part 4.7.)

- 3. Connect the new keyboard to the system PCB.

- 4. If normal operation is restored after connect the keyboard, the previous keyboard was defective. Assemble the system.

- 5. If normal operation is not restored, system PCB is probably defective. Refer to part 2.4.

## 2.8 PLASMA DISPLAY ISOLATION PROCEDURES

This section describes how to determine whether the PLASMA DISPLAY is defective or not. The procedures below are outlined in the following pages. They should be performed in the order indicated.

PROCEDURE 1: Display Check

PROCEDURE 2: Plasma Display Contrast and

Brightness Check

PROCEDURE 3: Display Test Execution

PROCEDURE 4: Plasma Display Connector Check

PROCEDURE 5: New PDP Connection

Display Check

- 1. Turn the POWER switch off.

- After turning the POWER switch on again, the following message should appear in the upper left-hand corner of the screen:

### MEMORY TEST XXXKB

- 3. If the message appears, go to PROCEDURE 2.

- 4. If the message does not appear, first do the following:

- (a) Confirm that the contrast and brightness volume is adjusted correctly.

- (b) Confirm that the display is not on an external CRT. (The CRT indicator lamp will be lit if the display is on an external CRT.)

- (C) Confirm that the DIP switch is OFF.

After confirming (a), (b) and (c) above, perform steps 1 and 2 again. If the message still fails to appear, go to PROCEDURE 3.

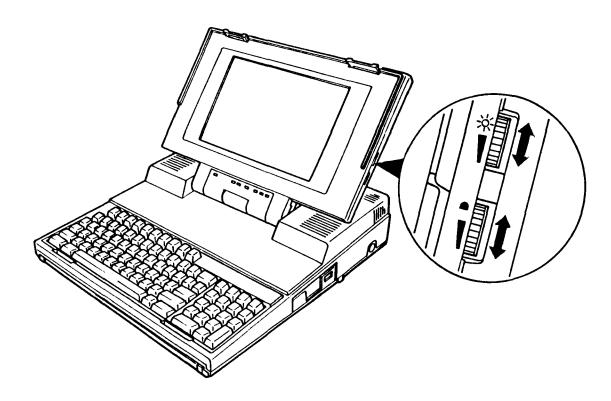

# Plasma Display Contrast and Brightness Check

- 1. Turn the contrast and brightness volume, then confirm that the screen becomes changed darker or brighter.

- 2. If the screen is changed darker or brighter, power supply inputs voltage to the PDP. Go to PROCEDURE 7.

- 3. If the screen is not changed, go to PROCEDURE 4.

FIGURE 2-8 Plasma Display Contrast and Brightness Check

Display Test Execution

- 1. Insert the diagnostics disk into the FDD and run the test and diagnostics programs.

- 2. If an error is generated during the display test from the diagnostics test menu, the system PCB is probably defective. Refer to part 2.4.

- 3. If no error is generated, the plasma display is normal.

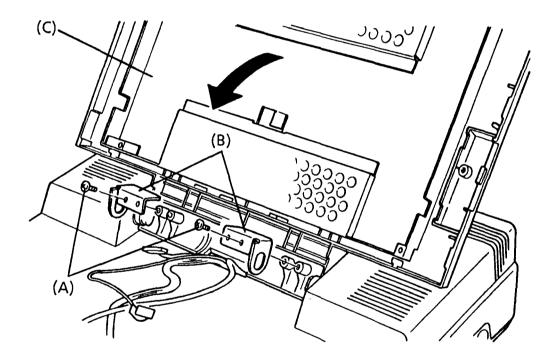

### PDP Connector Check

- 1. Turn the POWER switch off and unplug the ac cord.

- 2. Take out the PDP (Refer to part 4.4.) and confirm that the plasma display cable is connected securely to the module.

- 3. If the cable is connected securely, go to PROCEDURE 6.

- 4. If the cable is not connected securely, reconnect it.

FIGURE 2-9 PDP Connector Check

New PDP Connection

- 1. Connect a new PDP and plasma display cable to the PDP.

- 2. If normal operation is restored after replacing the PDP, the previous PDP was defective. Assemble the system.

- 3. If normal operation is not restored, system PCB is probably defective. System PCB is probably defective. Refer to part 2.4.

## 3.1 GENERAL

This part explains test and diagnostic programs. The purpose of the test and diagnostic programs is to check the functions of all hardware modules of the T3200 Personal Computer. There are 19 programs; they are composed of two modules: the service program module (DIAGNOSTICS MENU) and test program module (DIAGNOSTIC TEST MENU). The service program module is composed of 8 tasks:

- 1. HARD DISK FORMAT

- 2. SEEK TO LANDING ZONE (HDD)

- 3. HEAD CLEANING

- 4. LOG UTILITIES

- 5. RUNNING TEST

- 6. FDD UTILITIES

- 7. SYSTEM CONFIGURATION

- 8. SETUP

The test program module is composed of 11 tests as follows:

- 1. SYSTEM TEST

- 2. MEMORY TEST

- 3. KEYBOARD TEST

- 4. DISPLAY TEST

- 5. FLOPPY DISK TEST

- 6. PRINTER TEST

- 7. ASYNC TEST

- 8. HARD DISK TEST

- 9. REAL TIMER TEST

- 10. NDP TEST

- 11. EXPANSION TEST

The following items are necessary for carrying out the test and diagnostic programs.

- 1. T3200 Diagnostics disk

- 2. MS-DOS system disk

- 3. Work disk (formatted)

- 4. Cleaning disk kit

- 5. Printer wraparound connector

- 6. RS232C wraparound connector

The service engineer utilizes these programs to isolate problems by selecting the appropriate program and operation procedures described in the part 3.2 OPERATIONS.

# 3.2 OPERATIONS

- 1. Insert the diagnostics disk in the floppy disk drive and turn the POWER switch on.

- 2. Input **TESTCE3** for the **A>** prompt and press Enter.

- 3. The following display will appear.

```

TOSHIBA personal computer T3200 DIAGNOSTICS

Version X.XX (C) copyright TOSHIBA Corp. 1987

DIAGNOSTIC MENU :

1 - DIAGNOSTIC TEST

2 - HARD DISK FORMAT

3 - SEEK TO LANDING ZONE (HDD)

4 - HEAD CLEANING

5 - LOG UTILITIES

6 - RUNNING TEST

7 - FDD UTILITIES

8 - SYSTEM CONFIGURATION

9 - EXIT TO MS-DOS

0 - SETUP

PRESS [0] - [9] KEY

```

Detailed explanations of the service programs and the operations are given in parts 3.16 to 3.23.

4. Press 1 key then Enter. The following display will appear.

TOSHIBA personal computer T3200 DIAGNOSTICS version X.XX (C) copyright TOSHIBA Corp. 1987 DIAGNOSTIC TEST MENU : 1 - SYSTEM TEST 2 - MEMORY TEST 3 - KEYBOARD TEST 4 - DISPLAY TEST 5 – FLOPPY DISK TEST **6** – PRINTER TEST 7 - ASYNC TEST 8 – HARD DISK TEST 9 – REAL TIME TEST 10 - NDP TEST 11 - EXPANSION TEST 88 - FDD & HDD ERROR RETRY COUNT SET 99 - EXIT TO DIAGNOSTICS MENU PRESS [1] - [9] KEY

If you want to set the FDD and HDD retry count, type 88 then press Enter. The following message will appear. When don't operate, error retry count number is onece.

### FDD & HDD Error retry count ?

You can set the error retry count of the floppy disk test and hard disk test.

Type 99 then press Enter. Return to the DIAGNOSTICS MENU.

When select the FLOPPY DISK TEST, the following messages will appear.

Test drive number select (1:FDD1,2:FDD2,0:FDD1&2) ?

Media in drive#1 mode (1:360k,2:360k-1.2M/720k,3:1.2M,4:720k) ?

Test start track (Enter:0/dd:00-79) ?

In the case of type the test start track, test start track number of the floppy disk is one digit or two digits. When press Enter only, test start track number is zero track.

When select the HARD DISK TEST, the following message will appear.

Test drive number select (1:HDD1.2:HDD2.0:HDD1&2) ?

5. After pressing the test number (1 to 11) of the DIAGNOSTIC TEST MENU, the following display (sample) will appear.

TEST NAME XXXXXXX SUB TEST : XX PASS COUNT : XXXXX ERROR COUNT : XXXXX WRITE DATA : XX READ DATA : XX ADDRESS : XXXXX STATUS : XXX SUB-TEST MENU : 01 - ROM CHECKSUM : : 99 - Exit to DIAGNOSTIC TEST MENU SELECT SUB-TEST NUMBER ? TEST LOOP (1:YES/2:NO) ? ERRR STOP (1:YES/2:NO) ? -

6. Select the subtest number. Type the subtest number then press the Enter. The following message will appear. When select the KEYBOARD TEST, the following message will not appear.

TEST LOOP (1:YES/2:NO) ?

When select the (YES); Each time a test cycle ends, it increments the pass counter by one and repeats the test cycle.. When select the (NO); At the end of a test cycle, it terminares the test execution and exits to the subtest menu.

7. Type the 1 or 2 then press Enter. The following message will appear.

ERROR STOP (1:YES/2:NO) ?

When select the (YES); When an error occurs, it displays the error status and stops the execution of the test program. The operation guide displays on the right side of the display screen. When select the (NO); When an error occurs, it displays the error status then it increments the error counter by one and goes to the next test.

- 8. Type the 1 or 2 then press the Enter. The test program will run. Each subtest names described in the part 3.3.

- 9. When stop the test program, press Ctrl + Break keys then return to the DIAGNOSTICS MENU.

- 10. When error occurs on the test program, the following message will appear.

| ERROR STATUS NAME | [[ HALT OPERATION ]] |

|-------------------|----------------------|

|                   | 1: Test End          |

|                   | 2: Continue          |

|                   | 3: Retry             |

- 1: Terminates the test program execution and exits to the subtest menu.

- 2: Continues the test.

- 3: Retry the test.

The error code and error status names described in part 3.15.

# 3.3 SUBTEST NAMES

The following table shows subtest name of the test program.

| #          | TEST NAME               | SUBTEST#    | TEST ITEMS                       |

|------------|-------------------------|-------------|----------------------------------|

| 1          | SYSTEM                  | 01          | ROM checksum                     |

|            | J1 J1 E141              | 02          | HW status                        |

|            |                         | 01          | RAM constant data                |

|            |                         | <b>02</b> / | RAM address pattern data         |

| 2          | MEMORY                  | 03          | RAM refresh                      |

| •          |                         | 04          | Protected mode                   |

|            |                         | 05          | Protected mode (3MB)             |

|            |                         | 06          | LIM (Expansion memory)           |

| 3          | KEYBOARD                | 01          | Pressed key display              |

|            |                         | 02          | Pressed key code display         |

|            |                         | 01          | VRAM read/write                  |

|            |                         | 02          | Character attributes             |

|            |                         | 03          | Character set                    |

|            |                         | 04          | 80*25 Character display          |

| 4          | DISPLAY                 | 05          | Graphics display (color set 0/1) |

| 4          | DISPLAT                 | 06          | 640*200 Graphics display         |

|            |                         | 07          | 640*200 Graphics display         |

|            |                         | 08          | Display page                     |

|            |                         | 09          | "H" pattern display              |

|            |                         | 10          | Special attribute test           |

|            |                         | 01          | Sequential read                  |

|            |                         | 02          | Sequential read/write            |

| 5          | FDD<br>PRINTER<br>ASYNC | 03          | Random address/data              |

|            |                         | 04          | Write specified address          |

|            |                         | 05          | Read specified address           |

|            |                         | 01          | Ripple pattern                   |

| 6          | PRINTER                 | 02          | Function                         |

|            |                         | 03          | Wrapa around                     |

|            |                         | 01          | Wrap around (channel - 1)        |

|            |                         | 02          | Wrap around (channel - 2)        |

|            |                         | 03          | Point to point (send)            |

| 7          | ASYNC                   | 04          | Point to point (receive)         |

| <b>I</b> 1 |                         | 05          | Card modem loopback              |

|            |                         | 06          | Card modem on-line test          |

|            |                         | 07          | Dial tester test                 |

|            |                         | 01          | Sequential read                  |

|            |                         | 02          | Address uniquence                |

|            |                         | 03          | Random address/data              |

|            |                         | 04          | Cross talk & peek shift          |

| 8          | HDD                     | 05          | Write/read/compare(CE)           |

|            |                         | 06          | Write specified address          |

|            |                         | 07          | Read specified address           |

|            |                         | 08          | ECC circuit (CE cylinder)        |

|            |                         | 09          | Sequential write                 |

|            |                         | 01          | Real time test                   |

| 9          | REAL TIMER              | 02          | Backup memory test               |

|            |                         | 03          | Real time carry test             |

| 10         | NDP                     | 01          | NDP test                         |

|            | EXPANSION               | 01          | Box wrap around test             |

| 11         | UNIT                    | 02          | Box mono video ram test          |

|            |                         | 03          | Wrap around test ( 16bit bus)    |

TABLE 3-1 Subtest Names

## 3.4 SYSTEM TEST

Subtest 01 ROM checksum (Execution time: 1 second)

This test performs the ROM checksum test on the system PCB. (Test extent : F0000H - FFFFFH 64KB)

Subtest 02 H/W status

This test reads hardware status of the system, then displays the status as shown below.

76543210 H/W status = 10011101 Bit7 --- Display mode = Plasma Bit6 --- CPU clock = 12MHzBit5 --- Ten key PAD = 0FFBit4 --- 2MB FDD = 1.6MBBit3 --- Internal FDDs = 1 Bit2 --- Drive A/B = Normal Bit1 --- External FDD = OFF BitO --- Internal FDD = 2DD type [DIP] SW1 --- Auto SW = Disable --- Font Mode = Single SW4 SW6 --- European Font= Other SW7-10 --- Monitor Type = RGB 350

### 3.5 MEMORY TEST

Subtest 01 RAM constant data (Execution time: 30 seconds)

This test writes constant data to Memory, and then reads and compares them with the original data. The constant data are "FFFFH", "AAAAH", "5555H", "0101H" and "0000H".

Subtest 02 RAM address pattern data (Execution time: 10 seconds)

This test makes the segment address and offset address by XORing, and then writes the address pattern data and reads and compares them with the original data.

Subtest 03 RAM refresh (Execution time: 20 seconds)

This test writes constant data in 256 bytes length to Memory, and then reads and compares it with the original data. The constant data are "AAAAH" and "5555H". A certain interval time will be taken between the write and the read operations.

Subtest 04 Protected mode (Execution time: 78 seconds)

This test writes fixed data and address data to memory (256 kbytes to MAX 640 kbytes or 1 Mbytes to MAX. Mbytes) in protect mode, and then reads and compares it with the original data.

Subtest 05 Protected mode (3MB) (Execution time: 74 seconds)

This test writes fixed data and address data to memory (1 Mbytes to 4 Mbyts) in protect mode, and then reads and compares it with the original data.

Subtest 06 LIM (Expansion memory) (Execution time: 84 seconds)

Run the same test as subtest 04 for the expansion memory page frame address (D0000H) and the block select register (208H/218H) and memory size (3 Mbytes + 384 kbytes). This performed for every 64 kbytes.

### 3.6 KEYBOARD TEST

Subtest Ol Pressed key display

original state.

Note: Execute the test when Num-lock key is off. If this key is on, the test cannot be carried out.

When the keyboard layout (as shown below) is drawn on the display, press a certain key and check whether the corresponding key on the screen is changed to the character "\*". When the same key again, it becomes to be the original state so that it is able to confirm the self-repeat function. The following three keys are exceptions, and each key is changed to the character "\*" only when it is pressed, and if released, it gets back to the

### Ctrl key, Shift key, Alt key

| KEYBOARD TEST | IN PROGRESS       | 30100         |

|---------------|-------------------|---------------|

| KEIBOAND TEST | IN FROGRESS       | 20100         |

|               |                   |               |

|               | 500 E00           |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

|               |                   |               |

| IF TEST OK    | , PRESS [DEL] THE | N [ENTER] KEY |

Subtest 02 Pressed key code display

Scan code, character code, and key top name are displayed on the screen by pressing a certain key as shown below. Some keys such as Ins, Caps lock, Num lock, Scroll lock, Alt, Ctrl, and shift key blink on the screen when each one is pressed. Each scan code, character code and key top name described in the TABLE 3-2.(Next page)

KEYBOARD TESTIN PROGRESS302000Scan code=XXCharacter code=XXKeytop=XXXXIns LockCaps LockNum LockScroll LockAltCtrlLeft ShiftRight ShiftPRESS [ENTER] KEY

TABLE 3-2 Scan Code, Character Code, and Key Top Names

| KEY TOP                                 | SCAN CODE | CHARACTER<br>CODE |  |  |  |  |  |

|-----------------------------------------|-----------|-------------------|--|--|--|--|--|

| , , , , , , , , , , , , , , , , , , , , | 29        | 60                |  |  |  |  |  |

| 1                                       | 02        | 31                |  |  |  |  |  |

| 2                                       | 03        | 32                |  |  |  |  |  |

| 3                                       | 04        | 33                |  |  |  |  |  |

| 4                                       | 05        | 34                |  |  |  |  |  |

| 5                                       | 06        | 35                |  |  |  |  |  |

| 6                                       | 07        | 36                |  |  |  |  |  |

| 7                                       | 08        | 37                |  |  |  |  |  |

| 8                                       | 09        | 38                |  |  |  |  |  |

| 9                                       | 0A        | 39                |  |  |  |  |  |

| 0                                       | OB        | 30                |  |  |  |  |  |

| -                                       | 0C        | 2D                |  |  |  |  |  |

| =                                       | 0D        | 3D                |  |  |  |  |  |

| ١                                       | 2B        | 5C                |  |  |  |  |  |

| ←                                       | 0E        | 08                |  |  |  |  |  |

| $- \rightarrow$                         | OF        | 09                |  |  |  |  |  |

| q                                       | 10        | 71                |  |  |  |  |  |

| w                                       | 11        | 77                |  |  |  |  |  |

| е                                       | 12        | 65                |  |  |  |  |  |

| r                                       | 13        | 72                |  |  |  |  |  |

| t                                       | 14        | 74                |  |  |  |  |  |

| у                                       | 15        | 79                |  |  |  |  |  |

| u                                       | 16        | 75                |  |  |  |  |  |

| i                                       | 17        | 69                |  |  |  |  |  |

| 0                                       | 18        | 6F                |  |  |  |  |  |

| p                                       | 19        | 70                |  |  |  |  |  |

| [                                       | 1A        | 5B                |  |  |  |  |  |

| ]                                       | 1B        | 5D                |  |  |  |  |  |

| a                                       | 1E        | 61                |  |  |  |  |  |

| S                                       | 1F        | 73                |  |  |  |  |  |

| d                                       | 20        | 64                |  |  |  |  |  |

| f                                       | 21        | 66                |  |  |  |  |  |

| g                                       | 22        | 67                |  |  |  |  |  |

| h                                       | 23        | 68                |  |  |  |  |  |

| <u> </u>                                | 24        | 6A                |  |  |  |  |  |

| k                                       | 25        | 6B                |  |  |  |  |  |

|                                         | 26        | 6C                |  |  |  |  |  |

| i                                       | 27        | 3B                |  |  |  |  |  |

| ΚΕΥ ΤΟΡ       | SCAN CODE | CHARACTER<br>CODE |

|---------------|-----------|-------------------|

| ,             | 28        | 27                |

| Z             | 2C        | 7A                |

| X             | 2D        | 78                |

| C             | 2E        | 63                |

| v             | 2F        | 76                |

| b             | 30        | 62                |

| n             | 31        | 6E                |

| m             | 32        | 6D                |

| ,             | 33        | 2C                |

|               | 34        | 2E                |

| /             | 35        | 2F                |

| Space         | 39        | 20                |

| F2            | 3C        | 00                |

| F4            | 3E        | 00                |

| F6            | 40        | 00                |

| F8            | 42        | 00                |

| F10           | 44        | 00                |

| F1            | 3B        | 00                |

| F3            | 3D        | 00                |

| F5            | 3F        | 00                |

| F7            | 41        | 00                |

| F9            | 43        | 00                |

| Esc           | 01        | 1B                |

| Home          | 47        | 00                |

| ←             | 48        | 00                |

| End           | 4F        | 00                |

| Uper          | 48        | 00                |

| Lower         | 50        | 00                |

| Pg Up         | 49        | 00                |

| $\rightarrow$ | 4D        | 00                |

| Pg Dn         | 51        | 00                |

| Del           | 53        | 00                |

| Sys Req       | 85        | 00                |

| Prt Sc        | 37        | 2A                |

| -             | 4A        | 2D                |

| +             | 4E        | 2B                |

### 3.7 DISPLAY TEST

Subtest 01 VRAM read/write (Execution time: 1 second)

This test writes constant data (FFFFH, AAAAH, 5555H, 0000H) and address data to the video RAM (256 kbytes) and SRAM (2 kbytes); it then reads the data out and compares it the original data.

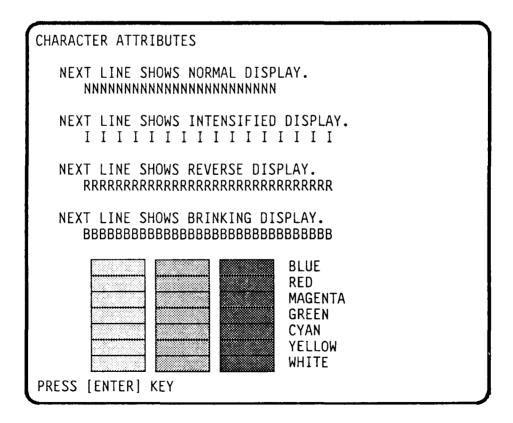

Subtest 02 Character attributes (Execution time: 1 second)

This test is for checking the various types of displays:

Normal Display Intensified Display Reverse Display Blinking Display In the case of color displays, all seven colors used (blue, red, magenta, green, cyan, yellow, white) are displayed. The background and foreground colors can then be checked for brightness. The display below appears on the screen when this test is run.

Subtest 03 Character set (Execution time: 1 second)

In this test the character code (00H to FFH) characters are displayed in the 40 x 25 pixel mode as shown below.

Subtest 04 80\*25 Character display (Execution time: 1 second)

In this test the shift caracters are displayed in the  $80 \times 25$  pixel mode as shown below.

| 7                                         |                   |

|-------------------------------------------|-------------------|

| 80*25 CHARACTER DISPLAY                   |                   |

| 0123456789012345678901234 678901234567890 |                   |

| !"#\$%&'()*+;/01234567 JXYZ[¥]^_`abcdef   | ghijklmn <b>a</b> |

| -!"#\$%&'()*+;/012345578 XYZ[¥]^_`abcdefg | hikkanaa          |

| "#\$%&'()*+,/012345678' (YZ[¥]^_`abcdefgh | i iklandog        |

| #\$%&'()*+;/0123456787 YZ[¥]^_ abcdefghi  | ikinnopa          |

| \$%&'()*+;/0123455789 Z[¥]^_`abcdefghij   |                   |

|                                           |                   |

|                                           |                   |

| &'()*+;/0123456789:;( ¥]^_`abcdefghijk    |                   |

| '()*+,/0123456789:;<= ]^_`abcdefghijklm   |                   |

| ()*+,/0123456789:;<=> `_`abcdefghijklmn   | OPERSTUVE         |

| )*+>/0123456789:;<=>?ā `abcdefghijklmno   |                   |

| *+;/0123456789:;<=>?@A _socdefghijklmnop  |                   |

| т,/0123456789:;<=>?ЗАВС сdefghijklmnара   |                   |

| PRESS [ENTER] KEY                         |                   |

| Theory Lenterly her                       |                   |

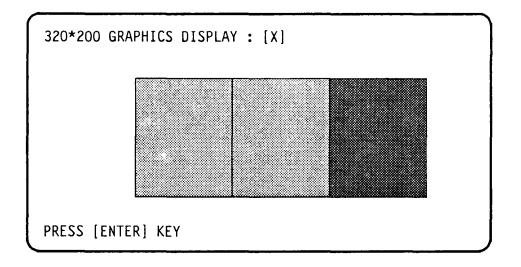

Subtest 05 320\*200 Graphics display (Execution time: 3 seconds)

This test displays two sets of color blocks for the color display in the 320 x 200 dots graphics mode (Mode 4 and D) as shown below. Color set 0: Green, red, yellow Color set 1: Cyan, Magenta, White

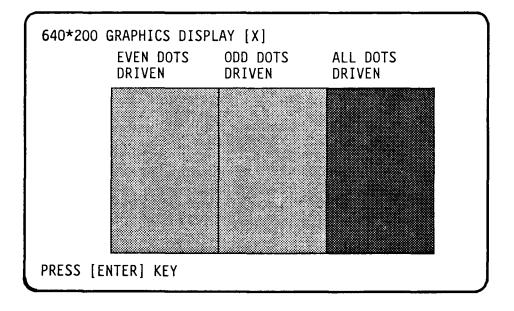

Subtest 06 640\*200 Graphics display (Execution time: 3 seconds)

This test displays the color blocks for the black and white display in the  $640 \times 200$  dot graphics mode (Mode 6 and E) as shown below.

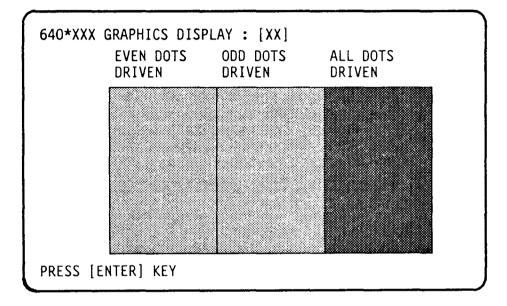

Subtest 07 640 x 400 Graphics display (Execution time: 5 seconds)

This test displays the color blocks for the black and white display in the  $640 \times 350$  and  $640 \times 400$  dot graphics mode (Mode 10/74) as shown below.

Note: Mode 74 is not applicable when the external display is selected.

Subtest 08 Display page (Execution time: 15 seconds)

This test confirms that the pages can be changed in order (page 0 to page 7) in the  $40 \times 25$  pixel mode.

| D.T.CI |          |   |   |   | ~ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|--------|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| DIS    |          |   |   |   |   | _ | _ |   |   | _ | _ |   |   |   |   |   |   | _ |   | _ | _ |   |   |   |

| (      | 0 C      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| (      | )        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

| (      | )        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

| (      | )        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

| (      | )        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

| (      | )        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

| (      | כ        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | Ō |

| Ċ      | Ĵ        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | õ |

| Ċ      | )        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | õ |

| Ċ      | ,        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ñ |

| Č      | ń        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ñ |

|        | ้ำ       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ñ |

|        | ,<br>,   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ň |

|        | ,<br>, , | ^ | 0 | ^ | 0 | 0 | 0 | 0 | ~ | ~ | 0 | 0 | 0 | ^ | 0 | ^ | 0 | ~ | 0 | ^ | ^ | ~ | ~ | 0 |

|        | JŪ       | 0 | υ | 0 | 0 | 0 | 0 | 0 | 0 | υ | U | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | U | 0 | 0 |

Subtest 09 "H" pattern display

This test displays H characters on the entire screen, as shown below.

Subtest 10 Special attribute test

This test displays the following display.

[ CRT/Caps/Num/Scroll LED test ]

(1) Press [ Caps Lock ] key! ...Caps (on/off)

(2) Press [ Num lock ] key! ...Num (on/off)

(3) Press [Scroll lock ] key! ...Scroll (on/off)

(4) Press [ Fn + End ] key! ...CRT (on)

(5) Press [ Fn + Home ] key! ...CRT (off)

Press [ENTER] KEY

## 3.8 FLOPPY DISK TEST

- **CAUTION:** Before running the floppy disk test prepare a formatted work disk and remove the diagnostics disk then insert the work disk to the FDD.

- Subtest 01 Sequential read (Execution time: 50 seconds)

This test performs a cyclic redundancy check with a continuous read operation of all track on a floppy disk. 2D (Double-sided, double density): Track 0 to 39 2DD (Double-sided, double density, double track): Track 0 to 79

Subtest 02 Sequential read/write (Execution time: 115 seconds)

This test writes data to all tracks (as defined above) continuously and then reads the data out and compares it to original data. (The data pattern is B5ADADH repeated.)

Subtest 03 Random address/data (Execution time: 12 seconds)

This test writes random data to random address on all tracks (as defined in subtest 01) and then reads the data out and compares it with the original data.

Subtest 04 Write specified address (Execution time: 1 second)

This test writes data specified by keyboard to tracks, heads, and address specified by the keyboard.

Subtest 05 Read specified address (Execution time: 1 second)

This test reads data from tracks, heads, and address specified by keyboard.

#### 3.9 PRINTER TEST

- **CAUTION:** A printer (IBM compatible) must be looked up to the system in order to execute the test.

- Subtest 01 Ripple pattern (Execution time: 110 seconds)

This test prints character for code 20H through 7EH line by line while shifting one character to the right at the beginning of each new line.

!"#\$%&'()\*+,-./0123456789:;<<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥]^\_\_`abcde "#\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥]`\_`abcder !"#\$%&'()\*+,-./0123456789:;<=>:@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥] \_\_abcdef !"#\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPORSTUVWXYZ[¥] \_\_abcdefg. !"#\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥]\_\_\_abcdefg. "#\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥]\_\_\_abcdefgh "#\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥] \_\_abcdef #\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPORSTUVWXYZ[¥] \_\_abcdef #\$%&'()\*+,-./0123456789··<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥] \_\_ abc \$%&'()\*+,-./0123456789··<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥] \_\_ abc DEFGHIJKLMNOFQRSTUVWXYZ[¥] %&'()\*+,-./01?<sup>^^</sup> MOPQRSTUVWXYZ[¥] &'()\*+ "WWXYZ [¥]

Subtest 02 Function (Execution time: 15 seconds)

> This test prints out various print type as shown below.

Normal Print Double Width Print Compressed Print Emphasized Print Double Strike Print All Characters Print PRINTER TEST 1. THIS LINES SHOWS NORMAL PRINT. THIS LINE SHOWS DOUBLE WIDTH PRINT. 2. THIS LINE SHOWS COMPRESSED PRINT.

THIS LINE SHOWS EMPASIZED PRINT.

THIS LINE SHOWS DOUBLE STRIKE PRINT.

- ALL CHARACTERS PRINT

!"#\$%&'()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[¥]^\_ abcdefgnijkimn opqrstuvwxyz(j)

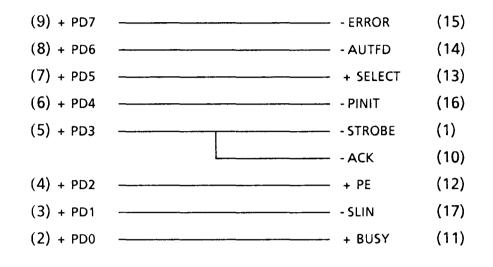

Subtest 03 Wrap around (Execution time: 1 second)

Note: A printer wraparound connector is necessary for executing this test. Wiring diagram of the printer wrap around connector described in the part 3.24.

> Checks the data, control, and status lines with the printer wrap around connector. Operations for the test is as follows.

> 1. After type the channel number, the following message will appear.

> > [[[ Change DIPSW-2 = ON ]]]?

- 2. Turn the DIP switch-2 on, then press Enter.

- 3. After finnished the test, turn the DIP switch-2 off.

#### 3.10 ASYNC TEST

For subtest 01 to subtest 05, transmission is done as follows in the communication.

Speed: 9600 BPS Data: 8 bits + parity (EVEN) l stop bit 20H to 7EH

Subtest 01 Wrap around (channel 1) (Execution time: 1 second)

Note: An RS232C wrap around connector must be connected to channel 1 to execute this test. RS232C wrap around connector wiring diagram described in part 3.24.

Performs a data send/receive test with the wrap around connector for the channel 1.

# Subtest 02 Wrap around (channel 2) (Execution time: 1 second)

Performs the same test as subtest 01 for the channel 2.

- Subtest 03 Point to point (send) (Execution time: 1 second)

- Note: This test can be executed on condition that the both send and receive sides are set in the same condition, and also connected together by RS232C direct cable (Wiring diagram described in part 3.22.). Subtest 03 must be executed together with subtest 04 and vice versa.